SCF FAPI 支持#

概述#

Aerial cuBB 支持小型蜂窝论坛定义的 5G FAPI 222.10.02。此版本支持大多数控制接口 (P5) 和数据路径接口 (P7) SCF 消息。

SCF FAPI 支持的消息#

下表总结了 SCF FAPI 支持的消息的状态。

SCF 消息 |

PDU 类型 |

SCF L2 适配器 |

SCF TestMAC |

使用 SCF TestMAC 和 RU 仿真器的 E2E |

|---|---|---|---|---|

DL_TTI.request |

PDCCH[9] |

是 |

是 |

是 |

PDSCH[7] |

是 |

是 |

是 |

|

CSI-RS[9] |

是 |

是 |

是[3] |

|

SSB[9] |

是 |

是 |

是 |

|

UL_TTI.request |

PRACH |

是 |

是 |

是 |

PUSCH[7] |

是 |

是 |

是 |

|

PUCCH[9] |

是 |

是 |

是 |

|

SRS[5][6][10] |

是 |

是 |

是 |

|

UL_DCI.request |

PDCCH:sup`[9]` |

是 |

是 |

是 |

SLOT 错误 |

否 |

否 |

否 |

|

TX_Data.request[1] |

PDSCH |

是 |

是 |

是 |

Rx_Data.indication[1] |

PUSCH(也包含 RNTI、HARQ Id、UL_CQI、Timing adv、RSSI) |

是 |

是 |

是 |

CRC.indication |

CRC |

是 |

是 |

是 |

UCI.indiaction |

PUSCH[8] |

是 |

是 |

是 |

PUCCH 格式 0,1 |

是 |

是 |

是 |

|

PUCCH 格式 2,3,4 |

是 |

是 |

仅 PF2 和 PF3 |

|

格式 0,1 的 SR |

是 |

是 |

是 |

|

格式 2,3,4 的 SR |

是 |

是 |

是[4] |

|

格式 0,1 的 HARQ |

是 |

是 |

是 |

|

格式 2,3,4 的 HARQ |

是 |

是 |

仅 PF2 和 PF3 |

|

CSI part 1 |

是 |

是 |

是 |

|

CSI part 2 |

是 |

是 |

仅 PUSCH |

|

RSSI 和 UL SINR 指标 |

是 |

是 |

PUSCH、PUSCH 上的 UCI 和 PF0,1,2,3 |

|

SRS.indication[5][6][10] |

SRS |

是 |

是 |

是 |

RACH.indication |

PRACH |

是 |

是 |

是 |

Config.request[2] |

是 |

是 |

||

Config.response |

是 |

是 |

||

Start.request |

是 |

是 |

||

Stop.request |

是 |

是 |

||

Stop.indication |

是 |

是 |

||

Error.indication |

是 |

是 |

||

Param.request |

否 |

否 |

||

Param.response |

否 |

否 |

注意[1]:SCF 实现基于 SCF_222.10.02,但以下例外情况除外

TX_DATA.request 和 RX_DATA.indication 的 PDU 长度更改为 32 位。这在 SCF_222.10.03 中定义。

当每个 PDU 中的 TLV 标签为 2 时,该实现支持每个 TTI 多个 UE。但是,TLV 中的偏移值将被忽略,L1 假定该时隙中的所有 TB 彼此相邻地放置在一个平面缓冲区中。

RX_DATA.indicationFAPI 消息在 NVIPC 消息的data_buf中包含 MAC PDU (TB 数据)。字段

类型

描述

TX_DATA.request

PDU 长度

uint16_t

PDU 描述和 PDU 数据的总长度(以字节为单位),不包括填充字节。值:0 → 65535

将类型更改为 uint32_t,取值范围为:0 ~ 2^32 -1

[NVIDIA 更改]:将其用作 PDU 数据(TB 数据)大小,不包括 PDU 描述。

RX_DATA.Indication

PDU 长度

uint16_t

PDU 的长度(以字节为单位)。长度为 0 表示 CRC 或解码错误。值:0 → 65535将类型更改为 uint32_t,取值范围为:0 ~ 2^32 -1

RX_DATA.Indication

PDU

可变

PDU 的内容。这将是 MAC PDU。

[NVIDIA 解决方法]:删除了此字段,请勿在 wireshark 解剖器中解析它。对于 SCF_222.10.04,尽管标签值设置为 1,但 MAC PDU 仍然在单独的 NVIPC 缓冲区中传递。

UL_TTI.request

SRFlag

uint8_t

指示 SR。仅对格式 0 和 1 有效。

[NVIDIA 解决方法]:增强功能,将其用作格式 2、3、4 的 BitLenSr。

注意[2]:支持带有供应商标签 0xA011 的预编码矩阵(表 3-33)。不支持数字波束表(表 3-32)。

注意[3]:对于 NZP CSI-RS,仅支持 4 个天线和单个 CSI-RS PDU。

注意[4]:当前实现支持 PUCCH 格式 2、3 和 1 上的多位 SR。由于 SCF FAPI 10.02 未显式提供任何字段来指示 UL_TTI.request 的 PUCCH_PDU 中的 SR 位长度,因此请使用 SRFlag 字段来提供 SR 位长度。例如,如果所需的 SR 位长度为 3,请设置 SRFlag = 3。

注意[5]:根据 SCF FAPI 222.10.02,支持 SRS.indication 和 UL_TTI.request 中的 SRS PDU。当 cuphycontroller_xxx.yaml 文件中设置了标志 enable_srs 时,可以启用 SRS,即 enable_srs: 1。

注意[6]:根据 SCF FAPI 222.10.04,也支持 SRS.indication 和 UL_TTI.request 中的 SRS PDU,这需要使用 “-DSCF_FAPI_10_04=ON” 构建选项启用,并且在 cuphycontroller_xxx.yaml 文件中设置标志 enable_srs,即 enable_srs: 1,如运行 cuBB 端到端中所述。

SRS.indication消息的格式在 SCF FAPI 222.10.04 表 3-129 中给出;报告 TLV 在表 3-130 中定义。支持的报告类型是表 3.132 中定义的用于码本或非码本 SRS 使用的归一化信道 I/Q 矩阵。

SRS 报告 TLV 标签为 1(自定义值),长度是实际报告大小(以字节为单位),不包括填充,值字段具有每个 SRS PDU 的 NVIPC 消息的 data_buf 部分的偏移量(以字节为单位)。报告数据放置在所有 SRS PDU 的 NVIPC 消息的

data_buf部分中。在宽带 SRS 的情况下,NVIPC 消息的 data_buf 部分可能没有足够的空间容纳所有 SRS PDU 的 SRS 信道向量。在这种情况下,Aerial 支持将 SRS.indication 拆分为多个消息。可以使用 CONFIG TLV 0x102B / indicationInstancesPerSlot 启用此功能,如 5G FAPI 222.10.04 规范表 3-36 中针对 PHY 配置所定义的那样。如果 L2 未启用此 TLV,并且 SRS.indication 无法容纳所有 SRS 信道向量,则 SRS.indication 将携带部分 SRS 信息。在处理此类 SRS PDU 时,会向 L2 发送错误指示,错误代码为 0x35,指示部分 SRS 指示。

表 3.131 FAPIv3 波束赋形报告,具有用于波束管理 SRS 使用的 PRG 级分辨率也受到支持。SRS 报告 TLV 标签为 2(自定义值),定义用于在

msg_buf中的值字段偏移 32 位处编码 SINR 报告,长度是实际报告大小(以字节为单位),不包括填充。此外,目前仅支持 2 的 PRG 大小。还支持组合使用波束管理 + 码本和波束管理 + 非码本。

在 FAPI 10.04 版本的 PDU 中添加了用户定义的参数

srsChestBufferIndex。更多详细信息请参见“注意 10”。

注意[7]:如果在 cuphycontroller_xxx.yaml 文件中设置了标志 mMIMO_enable,即 mMIMO_enable: 1 以启用动态波束赋形,则表示 L2 应编码 TX 预编码和波束赋形 PDU 和 RX 波束赋形 PDU,以包含用于 numPRGs、prgSize 和 digBFInterface 的字段,但 L2 不应编码 beamIdx,因为当使用动态波束赋形时,L2 没有可用的 beamIds 信息,但 L2 需要在 PDU 中提供其余信息给 L1。动态波束赋形:Tx 预编码和波束赋形 PDU 和 Rx 波束赋形 PDU 中的 digBFInterfaces = 0,并且不应为 Tx 预编码和波束赋形 PDU 编码进一步的参数,例如 PMidx、beamIdx,以及不应为 Rx 波束赋形 PDU 编码 beamIdx。这是由于包含 DL_TTI PDU 的 NVIPC msg_buf 的大小限制。

注意[8]:要在完整 PUSCH 时隙处理之前在 PUSCH 上的 UCI 的 UCI.indication 中获取 HARQ 值,L2 应根据 SCF FAPI 222.10.04 中的表 3-36 包含 PHY 配置 TLV 0x102B (indicationInstancesPerSlot),并将 UCI.indication 设置为 2。如果在 config.request 中将任何小区的 UCI.indication 设置为 2,则将为所有小区激活早期 HARQ 功能。

注意[9]:对于应用在小区配置请求中的 FAPI 10.02 表 3-61 数字波束表 (DBT) PDU 中接收到的静态波束权重,用于 Tx 预编码和波束赋形 PDU 和 Rx 波束赋形 PDU 中发送的 beamId,我们需要使用 -DENABLE_STATIC_BFW=ON 进行编译,并且应在 l2_adapter_config_xxx.yaml 中设置 enable_beam_forming。对于静态波束赋形:Tx 预编码和波束赋形 PDU 和 Rx 波束赋形 PDU 中的 digBFInterfaces != 0。静态波束赋形权重应用允许的 BeamId 范围为 1 到 1024,其余 BeamId 用于动态波束赋形权重。

注意[10]:以下是为 SRS 缓冲区索引实施的更改,预计将由 L2 处理。

L1 将预先分配 256 个固定大小的缓冲区来存储 SRS 信道估计。

如果未发送,则 L2 可以为少于 256 个缓冲区配置 TLV 0xA019 - NUM_SRS_CHEST_BUFFERS (uint32_t),否则默认情况下将为每个小区分配 256 个缓冲区。

L2 应在所有活动 UE 之间管理这些缓冲区索引。

L2 应在 UL_TTI SRS PDU 的 srsChestBufferIndex 字段中指定缓冲区索引。

L1 将在相应的 SRS.IND 中响应相同的缓冲区索引 (srsChestBufferIndex)。

L2 还需要在 DLBFW_CVI.request/ ULBFW_CVI.request 的 srsChestBufferIndex 字段中指定 SRS CH_EST 缓冲区索引,L1 将使用该索引作为动态波束赋形权重计算的输入。

如果 L2 为任何 SRS PDU 配置了相同的缓冲区索引 (srsChestBufferIndex),而该 PDU 对应的缓冲区 SRS.INDICATION 之前未收到,则在这种情况下将报告错误指示。

如果 L2 在 DLBFW_CVI.request/ ULBFW_CVI.request 中发送了 SRS 缓冲区索引 (srsChestBufferIndex),而该索引的 SRS.INDICATION 尚未发送,则 cuPHY 中将报告错误,并且该请求将被丢弃。

供应商特定消息#

在 22-4 版本之后,添加了一个新的供应商特定消息 SLOT.response。在 22-4 版本之前,L2 必须使用 nvIPC 通知功能设置事件,以在发送最后一个 FAPI 消息后通知 L1 关于“EOM”。这对于单小区以及所有 FAPI 消息都准时的情况下效果良好。L1 也使用 nvIPC 通知功能在发送每条消息后设置事件。

新的 SLOT.response FAPI 消息被 L2 用作每个时隙中每个小区的最后一个 FAPI 消息。它具有以下优点

它可以作为每个时隙中每个小区的“EOM”。

每个小区都发送

SLOT.response作为每个时隙的最后一个 FAPI 消息。即使在空时隙(即没有调度的时隙)中,L2 也应发送

SLOT.response。“虚拟”或空 DL/UL TTI 是可选的/不需要的。

来自 L2 的通知事件是可选的/不需要的。

SLOT.response 消息格式如下所示

/************************************************

* Slot.response

***********************************************/

typedef struct

{

scf_fapi_body_header_t msg_hdr;

uint16_t sfn;

uint16_t slot;

} __attribute__ ((__packed__)) scf_fapi_slot_rsp_t;

Message-id 0x8F is used for this message

{ …

SCF_FAPI_RX_PRACH_INTEFERNCE_INDICATION = 0x8E,

SCF_FAPI_SLOT_RESPONSE = 0x8F,

SCF_FAPI_RESV_2_END = 0xFF,

} scf_fapi_message_id_e;

L1 continues to send a notify event after all FAPI messages to L2 to minimize impact on L2.

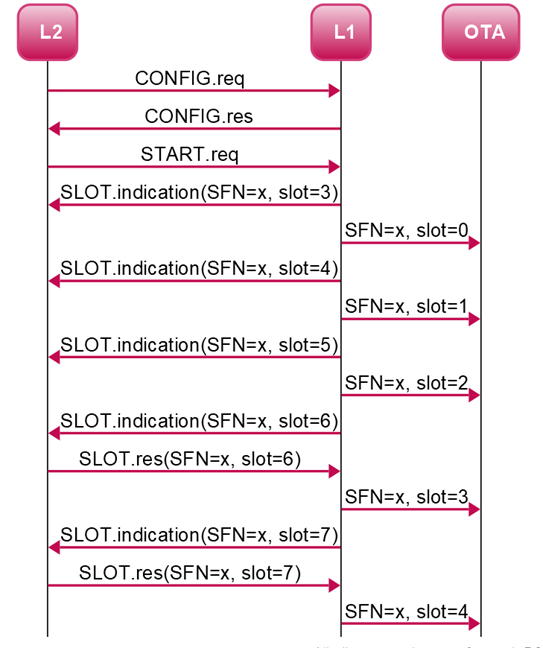

消息序列#

消息序列示例如下所示

注意

在收到第一个 SLOT.indication 时,L2 无法在 2-3 个时隙内发送 SLOT.response,因为它具有 3 个时隙的提前量。

延迟消息的影响#

所有消息对于一个小区都迟到(DL_TTI+TX_DATA+UL_DCI 或 UL_TTI)

所有消息都为所述小区丢弃。对其他小区没有影响。

DL_TTI 准时到达,但 TX_DATA.request 对于一个小区迟到

这被视为部分时隙。由于小区分组,所有小区的 PDSCH 和 DL-PDCCH 都被丢弃。

UL_TTI 对于一个小区迟到

ULSCH 不会为所述小区处理。对其他小区没有影响。

UL_DCI 对于一个小区迟到

UL-PDCCH 不会为所述小区处理。对其他小区没有影响。

SLOT.response对于一个小区迟到所有及时收到的 FAPI 消息都将为该小区处理。

如何启用或禁用 SLOT.response#

此功能在 23-1 版本之后的 L1 中默认启用。在与 L2 集成时,L2 需要以如上所述的方式发送此供应商特定消息。

选项 ENABLE_L2_SLT_RSP 应在 L1、L2 和 libnvipc.so 独立构建中配置相同的值,以用于 L2。有关详细信息,请参阅 cuBB 快速入门指南。

如果 L2 不支持 SLOT.response 消息,请通过在 cmake 命令中设置 “-ENABLE_L2_SLT_RSP=OFF” 标志来禁用此功能

cmake <existing flags> -DENABLE_L2_SLT_RSP=OFF

启用该功能后,以下情况属实

L2 必须发送供应商特定的

SLOT.response消息作为每个小区的最后一个 FAPI 消息。L2 即使在空时隙(未调度任何内容的时隙)中也要发送此消息。

allowed_fapi_latency已弃用,并假定为 0。L2 必须在 L1 的

SLOT.indication标记的 500 us 时间预算内完成发送所有 FAPI 消息。延迟的 FAPI 消息将被丢弃。

空时隙中的“虚拟” DL/UL TTI 消息是可选的。

发送所有 FAPI 消息后的通知事件是可选的。

L2 适配器配置文件中的

ipc_sync_mode已弃用。

L1 将继续在所有 FAPI 消息之后发送通知事件,以最大限度地减少对 L2 的影响。

64T64R 的动态波束赋形#

要在 Aerial 软件中启用此功能,应在

cuphycontroller_xxx.yaml文件中设置/引入标志mMIMO_enable,即mMIMO_enable: 1。CONFIG.req 中需要两个额外的 TLV

- TLV 0xA016,表示 NUM_TX_PORT (uint8_t)

此字段指定 PHY 的 DL BB 端口数。5G FAPI 222.10.04 在表 3-37 中将字段 numTxAnt 和 numRxAnt 描述为 - “numTxAnt 不能超过 PHY 的 DL BB 端口数”。因此,表 3-37 中的字段表示逻辑天线端口。

5G FAPI 223 将基带端口描述为层到 RU TX/RX 端口之间的映射。PHY 需要从 L2 了解 BB 端口(参见 SCF-223.2.0.4 中的图 3-3)。

PHY 将使用此字段来读取 DL BB 端口的数量。

如果未从 L2 收到 TLV,并且在

cuphycontroller_xxx.yaml文件中设置了标志mMIMO_enable,即mMIMO_enable: 1,则 DL BB 端口数的默认值设置为 8。

- TLV 0xA017,表示 NUM_RX_PORT (uint8_t)

此字段指定 PHY 的 UL BB 端口数。5G FAPI 222.10.04 在表 3-37 中将字段 numTxAnt 和 numRxAnt 描述为 - “numRxAnt 不能超过 PHY 的 UL BB 端口数”。因此,表 3-37 中的字段表示逻辑天线端口。

5G FAPI 223 将基带端口描述为层到 RU TX/RX 端口之间的映射。PHY 需要从 L2 了解 BB 端口(参见 SCF-223.2.0.4 中的图 3-3)。

PHY 将使用此字段来读取 UL BB 端口的数量

如果未从 L2 收到 TLV,并且在

cuphycontroller_xxx.yaml文件中设置了标志mMIMO_enable,即mMIMO_enable: 1,则 UL BB 端口数的默认值设置为 4。

DL 和 UL TTI 都有一个为 TRP 方案添加的附加字段。请参阅 SCF FAPI 支持的消息部分中的注意 6

动态波束赋形仅支持 PDSCH 和 PUSCH

在 S-slot 上调度了 SRS 的 UE 不应在后续的 D 和 U 时隙中调度 PDSCH 和 PUSCH 的动态波束赋形,直到收到该 UE 的 SRS 指示为止。这可以防止 L1 和 L2 之间的竞争条件,在这种情况下,SRS 信道向量已在 GPU 托管的内存中更新,但最新的 SRS 信道向量尚未发送到 L2。在这种情况下,L2 可能会根据过时的 SRS 信道向量做出调度决策,并且 BFW 计算可能会使用刷新的 SRS 信道向量进行。

已定义来自 L2 到 L1 的两个新的 FAPI 消息,以在 L1 中实现波束赋形权重计算,如下所示

SCF_FAPI_DL_BFW_CVI_REQUEST = 0x90

SCF_FAPI_UL_BFW_CVI_REQUEST = 0x91

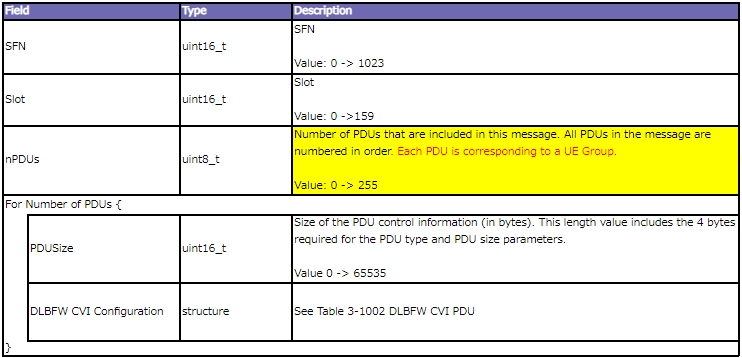

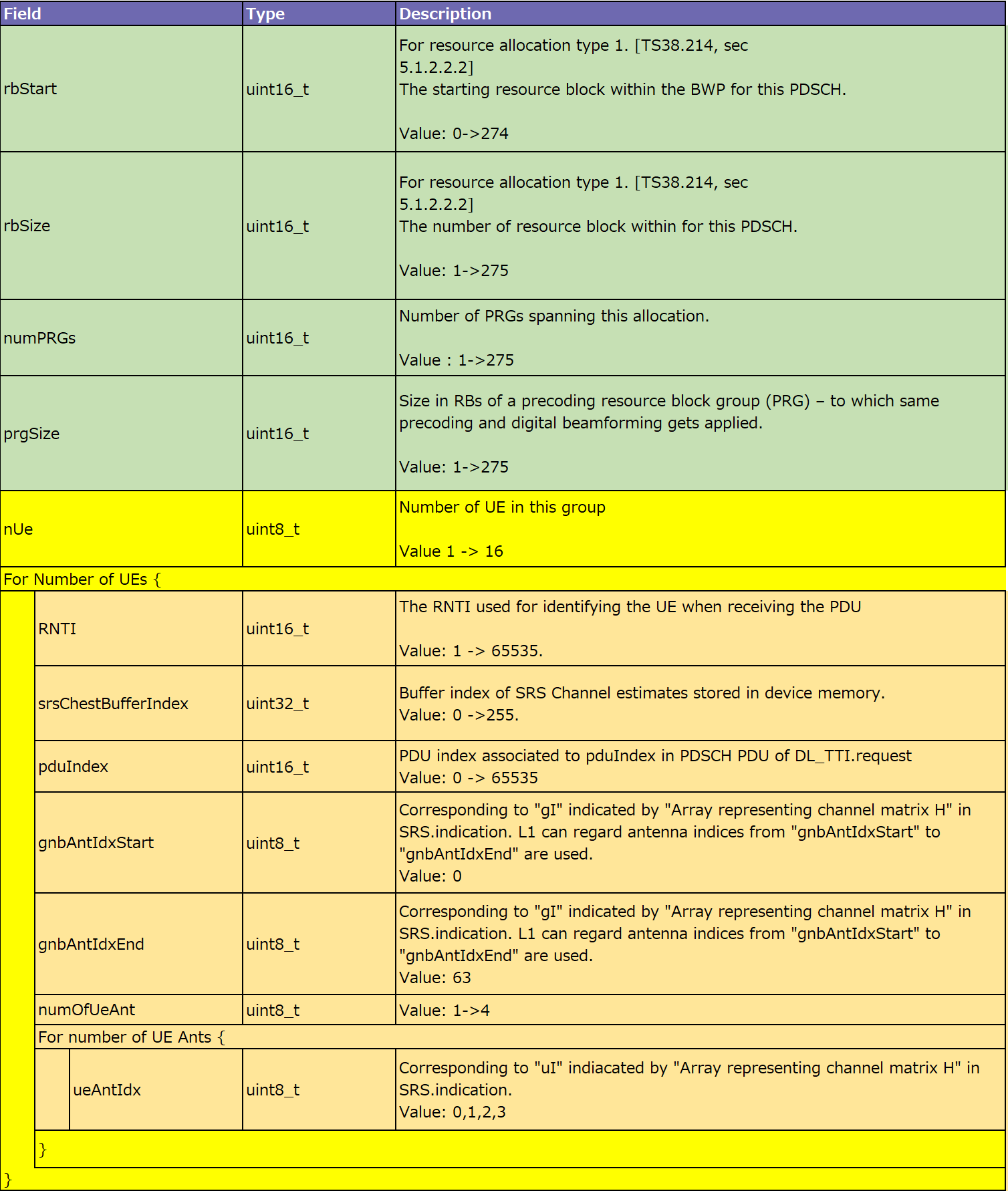

来自 L2 到 L1 的 FAPI 消息的结构用于波束赋形权重计算如下。相同的消息结构用于 DL(PDSCH) 和 UL(PUSCH)。当用于 DL(PDSCH) 时,它被称为 DLBFW_CVI.request,当用于 UL(PUSCH) 时,它被称为 ULBFW_CVI.request。

表 3-1001 DLBFW_CVI.request 消息体

表 3-1002 DLBFW CVI PDU

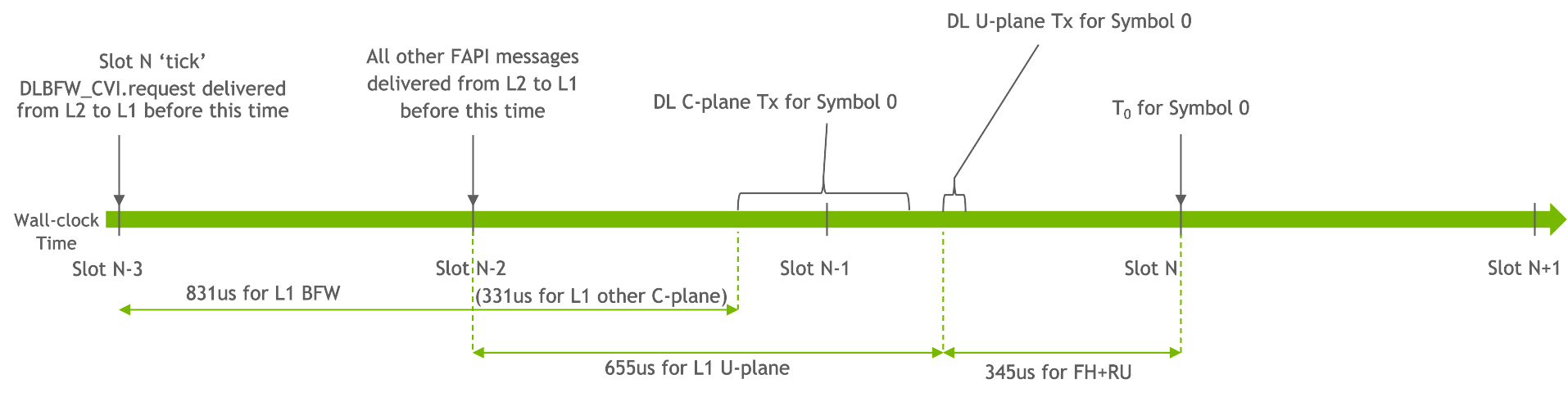

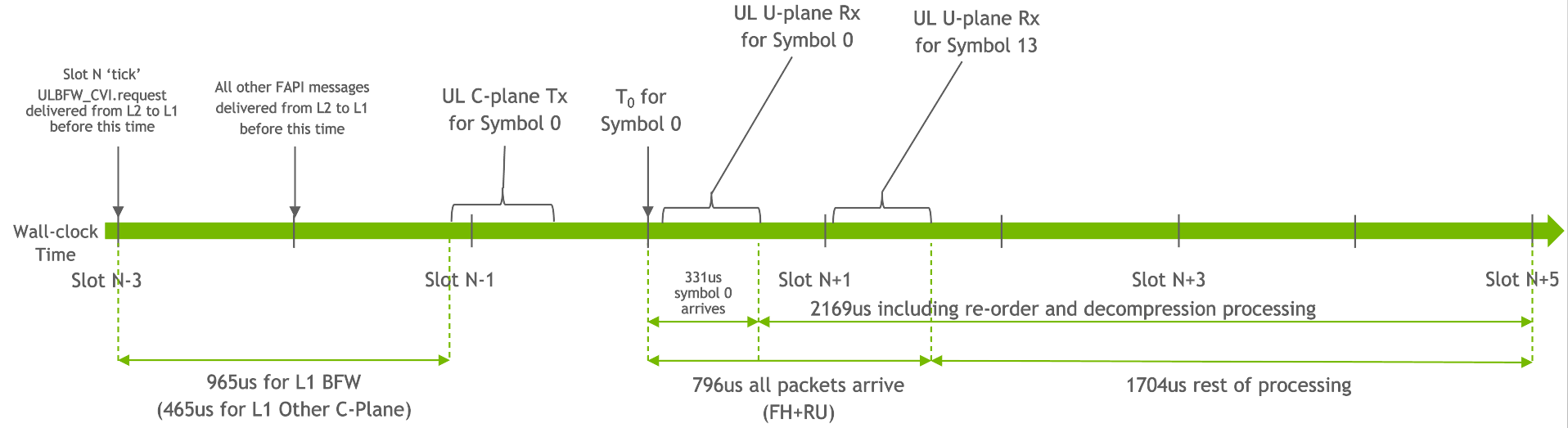

接收 DLBFW_CVI.request 和 ULBFW_CVI.request 的时间线如下所示

时隙 N 的下行链路时间线

时隙 N 的上行链路时间线 - PUSCH/PUCCH/PRACH

64T64R 的静态波束赋形#

CONFIG.req中需要一个额外的 TLVTLV 0xA010 DIGITAL_BEAM_TABLE_PDU (uint8_t)

当需要编码 DBT PDU 时,此 TLV 在 Cell_Config 请求中使用,其中包含将用于某些信道的静态波束赋形权重。

“固定 RTW”及其对应的权重来自 FAPI 10.02 表 3-61 数字波束表 (DBT) PDU。

定义了一个新的更大的 NVIPC 缓冲区池(

cpu_large: {buf_size: 4096000, pool_len: 64}),以在单个缓冲区中存储整个 DBT PDU。相同的缓冲区池应用于编码和发送 FAPI 10.02 表 3-61 数字波束表 (DBT) PDU。仅当在

l2_adapter_config_xxx.yaml中设置enable_beam_forming时,才能处理或存储 DBT PDU。

从 L1 到 L2 的 ERROR.indication 中报告的其他 Aerial 特定错误代码#

从值 0x33 开始,添加了其他 Aerial 特定错误代码,L2 可能会在从 L1 到 L2 的 ERROR.indication 消息中收到这些错误代码。以下是一个示例

SCF_ERROR_CODE_FAPI_END = 0x32,

//Vendor specific error codes ---- begin

SCF_ERROR_CODE_L1_PROC_OBJ_UNAVAILABLE_ERR = 0x33,

SCF_ERROR_CODE_MSG_LATE_SLOT_ERR = 0x34, //Indicates that L1's timer thread did not wake up on the slot boundary and slot indication for the indicated SFN,slot is late and will not be sent from L1 to L2

SCF_ERROR_CODE_PARTIAL_SRS_IND_ERR = 0x35, //Indicates partial SRS indication

SCF_ERROR_CODE_L1_DL_CPLANE_TX_ERROR = 0x36, //Indicates a DL C-plane trasmission error (Timing/Functional)

SCF_ERROR_CODE_L1_UL_CPLANE_TX_ERROR = 0x37, //Indicates a UL C-plane trasmission error (Timing/Functional)

SCF_ERROR_CODE_L1_DL_GPU_ERROR = 0x38, //Indicates a DL GPU pipeline processing error

SCF_ERROR_CODE_L1_DL_CPU_TASK_ERROR = 0x39, //Indicates a DL CPU Task incompletion error

SCF_ERROR_CODE_L1_UL_CPU_TASK_ERROR = 0x3A, //Indicates a UL CPU Task incompletion error

SCF_ERROR_CODE_L1_P1_EXIT_ERROR = 0x3B, //Indicates Part 1 of the error indication during L1 app exit process

SCF_ERROR_CODE_L1_P2_EXIT_ERROR = 0x3C, //Indicates Part 2 of the error indication during L1 app exit process post cudaDeviceSynchronize if CUDA coredump env variables are set

SCF_ERROR_CODE_L1_DL_CH_ERROR = 0x3D, //Indicates DL channel run (CPU/GPU) error

SCF_ERROR_CODE_L1_UL_CH_ERROR = 0x3E //Indicates UL channel run (CPU/GPU) error