时钟和复位

系统中有 3 个主要时钟:主机接口 (hif) 时钟、APB 时钟和传感器接口 (sif) 时钟。

主机接口信号连接到以太网 MAC 以发送或接收数据。因此,主机接口带宽(时钟频率 x 数据宽度)应支持设计的以太网带宽。

例如,在 10G 应用中集成 Holoscan 传感器桥 IP 时,常用的时钟频率和数据宽度分别为 156.25MHz 和 64 位。如果系统以太网 MAC 输出 156.25MHz,一种可能的设计是使用相同的以太网 MAC 输出时钟作为主机接口时钟。如果系统无法直接使用以太网 MAC 时钟,则可以使用双时钟 FIFO 来匹配以太网 MAC 的带宽。最终,时钟架构取决于 Holoscan 传感器桥 IP 的预期应用和所使用的 FPGA 供应商。

传感器接口时钟 (i_sif_clk) 是驱动前端传感器 AXI-Stream 接口的时钟。

传感器 AXI-Stream 信号使用 Holoscan 传感器桥 IP 内的双时钟 FIFO 跨越到主机接口时钟域。

Holoscan 传感器桥 IP 从 1 个主要异步复位输入输出与各自时钟同步的复位信号。

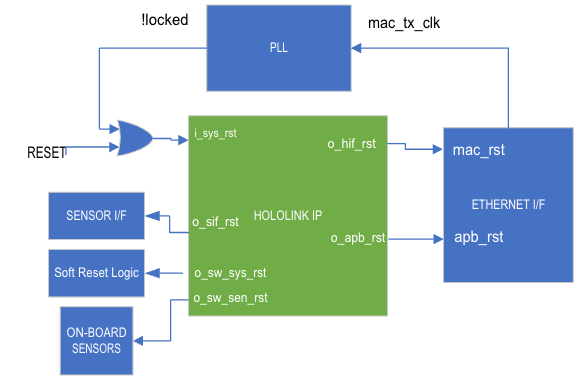

输入复位端口 (i_sys_rst) 是一个高电平有效、异步复位。此端口应连接到与 PLL 锁定信号门控的板载复位引脚(RESET,高电平有效,在图中)。这将向 Holoscan 传感器桥 IP 断言复位,直到 PLL 锁定。

输入和输出复位的示例连接如下所示。

图 1 参考设计复位连接

下表描述了各种输出复位及其在断言和解除断言时的时钟关系。

表 1 复位断言和解除断言

复位 | 断言 | 解除断言 | 描述 |

|---|---|---|---|

| o_apb_rst | 异步 | 与 i_apb_clk 同步 | 可用于复位 IP 外部的 APB 逻辑 |

| o_hif_rst | 异步 | 与 i_hif_clk 同步 | 可用于复位 IP 外部的主机逻辑 复位在 o_apb_rst 解除断言后解除断言。 |

| o_sif_rst | 异步 | 与 i_sif_clk 同步 | 可用于复位 IP 外部的传感器接口逻辑 复位在 o_apb_rst 解除断言后解除断言。 |

| o_sw_sen_rst | 与 i_hif_clk 同步 | 与 i_hif_clk 同步 | 寄存器控制的传感器复位。 可以连接到 FPGA I/O 以复位板载传感器。 |

| o_sw_sys_rst | 与 i_hif_clk 同步 | 与 i_hif_clk 同步 | 寄存器控制的系统复位。可用于复位系统级逻辑。 这也将触发 o_hif_rst、o_apb_rst 和 o_sif_rst 的复位。 |