Parallel Thread Execution ISA 版本 8.7

使用 PTX(Parallel Thread Execution)和 ISA(指令集架构)的编程指南。

1. 简介

本文档描述了 PTX,一种低级并行线程执行虚拟机和指令集架构 (ISA)。PTX 将 GPU 公开为数据并行计算设备。

1.1. 使用 GPU 的可扩展数据并行计算

在对实时、高清晰度 3D 图形的巨大市场需求的驱动下,可编程 GPU 已经发展成为高度并行、多线程、多核处理器,具有强大的计算能力和极高的内存带宽。GPU 特别适合解决可以表达为数据并行计算的问题——相同的程序并行地在多个数据元素上执行——且具有高算术强度——算术运算与内存运算的比率。由于每个数据元素都执行相同的程序,因此对复杂流程控制的需求较低;并且由于它在许多数据元素上执行并具有高算术强度,因此内存访问延迟可以通过计算而不是大数据缓存来隐藏。

数据并行处理将数据元素映射到并行处理线程。许多处理大型数据集的应用程序可以使用数据并行编程模型来加速计算。在 3D 渲染中,大量的像素和顶点被映射到并行线程。类似地,图像和媒体处理应用程序,如渲染图像的后处理、视频编码和解码、图像缩放、立体视觉和模式识别,可以将图像块和像素映射到并行处理线程。事实上,许多图像渲染和处理领域之外的算法也通过数据并行处理得到加速,从通用信号处理或物理模拟到计算金融或计算生物学。

PTX 为通用并行线程执行定义了一个虚拟机和 ISA。PTX 程序在安装时被翻译成目标硬件指令集。PTX 到 GPU 的转换器和驱动程序使 NVIDIA GPU 能够用作可编程并行计算机。

1.2. PTX 的目标

PTX 为通用并行编程提供了一个稳定的编程模型和指令集。它旨在在支持 NVIDIA Tesla 架构定义的计算特性的 NVIDIA GPU 上高效运行。CUDA 和 C/C++ 等高级语言编译器生成 PTX 指令,这些指令经过优化并转换为本机目标架构指令。

PTX 的目标包括以下内容

提供一个跨越多个 GPU 世代的稳定 ISA。

在编译后的应用程序中实现与本机 GPU 性能相当的性能。

为 C/C++ 和其他编译器提供一个与机器无关的 ISA 作为目标。

为应用程序和中间件开发人员提供代码分发 ISA。

为优化代码生成器和转换器提供一个通用的源代码级 ISA,这些生成器和转换器将 PTX 映射到特定的目标机器。

方便手动编写库、性能内核和架构测试。

提供一个可扩展的编程模型,该模型可以跨越从单个单元到多个并行单元的 GPU 尺寸。

1.3. PTX ISA 版本 8.7

PTX ISA 版本 8.7 引入了以下新功能

增加了对

sm_120目标架构的支持。增加了对支持专门加速功能的

sm_120a目标的支持。扩展了

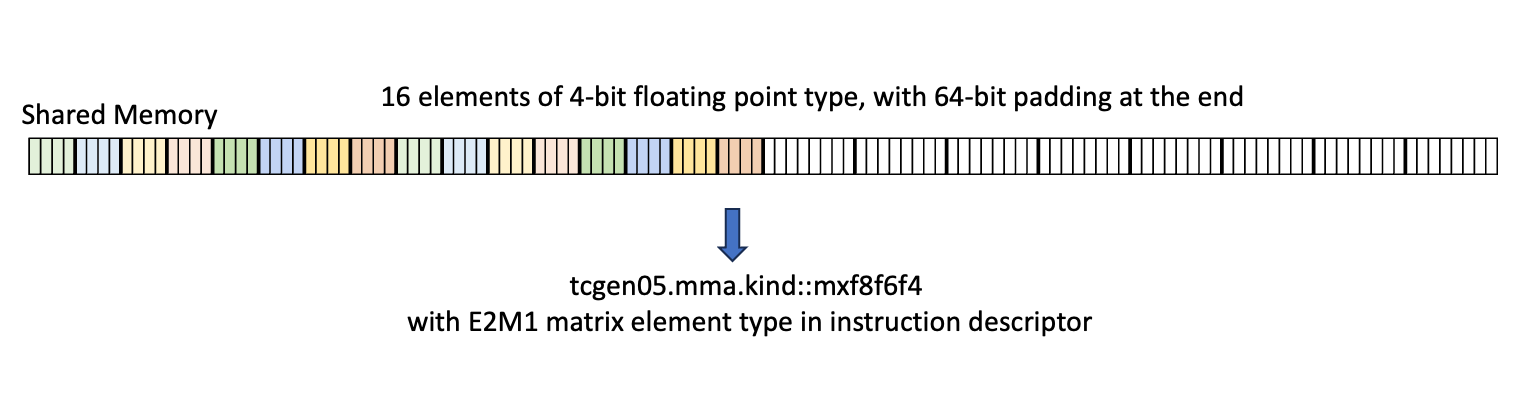

tcgen05.mma指令,以增加对.kind::mxf4nvf4和.scale_vec::4X限定符的支持。扩展了

mma指令,以支持.f16类型累加器和形状.m16n8k16以及 FP8 类型.e4m3和.e5m2。扩展了

cvt指令,以增加对.rs舍入模式和目标类型.e2m1x4、.e4m3x4、.e5m2x4、.e3m2x4、.e2m3x4的支持。扩展了对

st.async和red.async指令的支持,以增加对.mmio、.release、.global和.scope限定符的支持。扩展了

tensormap.replace指令,以增加对.elemtype限定符的值13到15的支持。扩展了

mma和mma.sp::ordered_metadata指令,以增加对类型.e3m2/.e2m3/.e2m1和限定符.kind、.block_scale、.scale_vec_size的支持。

1.4. 文档结构

本文档中的信息组织成以下章节

编程模型 概述了编程模型。

PTX 机器模型 概述了 PTX 虚拟机模型。

语法 描述了 PTX 语言的基本语法。

状态空间、类型和变量 描述了状态空间、类型和变量声明。

指令操作数 描述了指令操作数。

抽象 ABI 描述了函数和调用语法、调用约定以及 PTX 对抽象应用程序二进制接口 (ABI) 的支持。

指令集 描述了指令集。

特殊寄存器 列出了特殊寄存器。

指令 列出了 PTX 中支持的汇编指令。

发行说明 提供了 PTX ISA 2.x 及更高版本的发行说明。

参考文献

-

754-2008 IEEE 浮点运算标准。ISBN 978-0-7381-5752-8, 2008。

-

OpenCL 规范,版本:1.1,文档修订版:44,2011 年 6 月 1 日。

-

CUDA 编程指南。

https://docs.nvda.net.cn/cuda/cuda-c-programming-guide/index.html

-

CUDA 动态并行编程指南。

https://docs.nvda.net.cn/cuda/cuda-c-programming-guide/index.html#cuda-dynamic-parallelism

-

CUDA 原子性要求。

https://nvda.org.cn/cccl/libcudacxx/extended_api/memory_model.html#atomicity

-

PTX 互操作性编写指南。

https://docs.nvda.net.cn/cuda/ptx-writers-guide-to-interoperability/index.html

2. 编程模型

2.1. 高度多线程的协处理器

GPU 是一种能够并行执行大量线程的计算设备。它作为主 CPU 或主机 的协处理器运行:换句话说,主机上运行的应用程序的数据并行、计算密集型部分被卸载到设备上。

更准确地说,一个应用程序中被多次执行但独立于不同数据的部分,可以隔离到一个内核函数中,该函数在 GPU 上作为许多不同的线程执行。为此,这样的函数被编译成 PTX 指令集,并且生成的内核在安装时被翻译成目标 GPU 指令集。

2.2. 线程层次结构

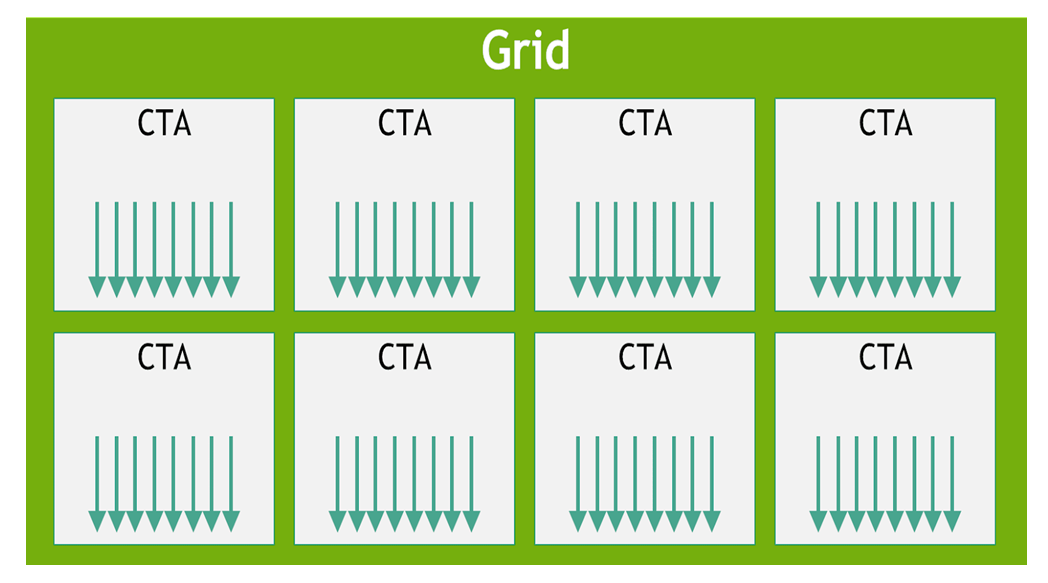

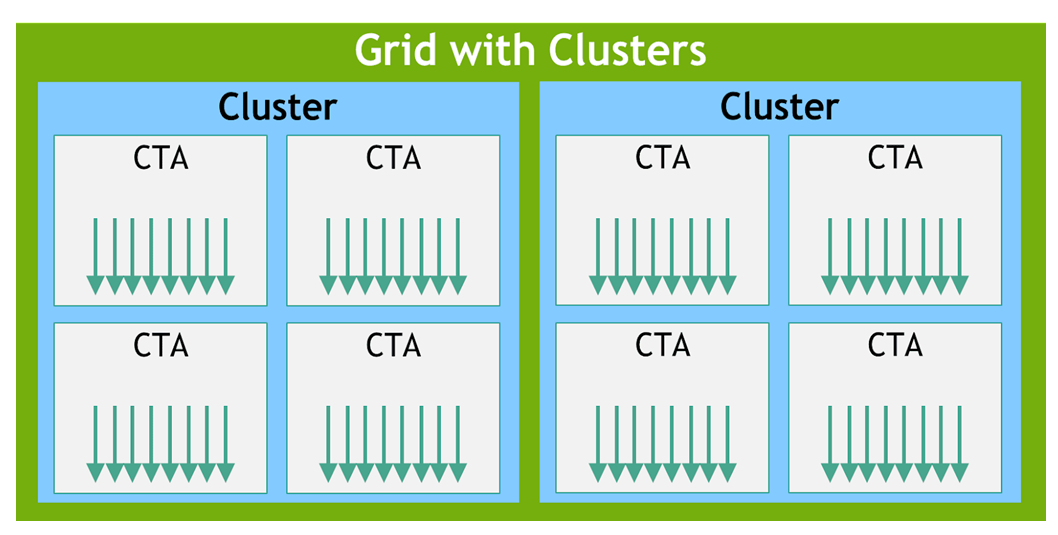

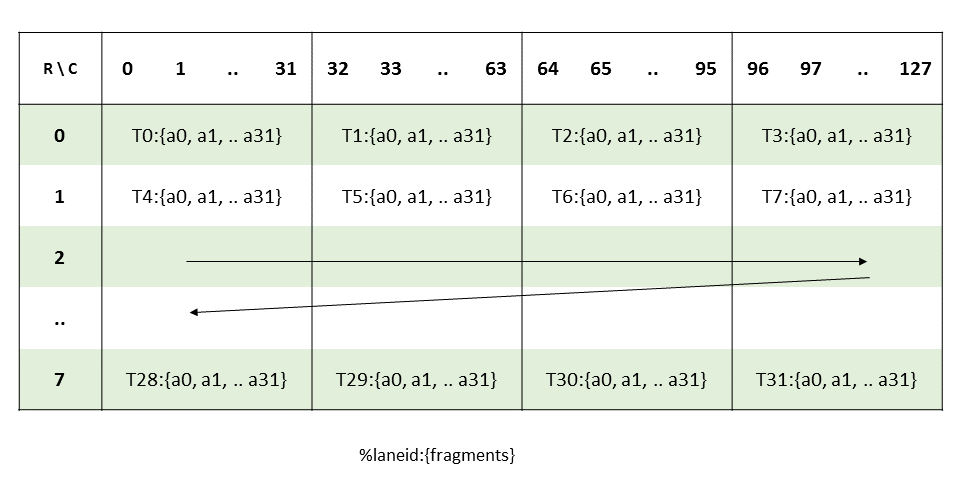

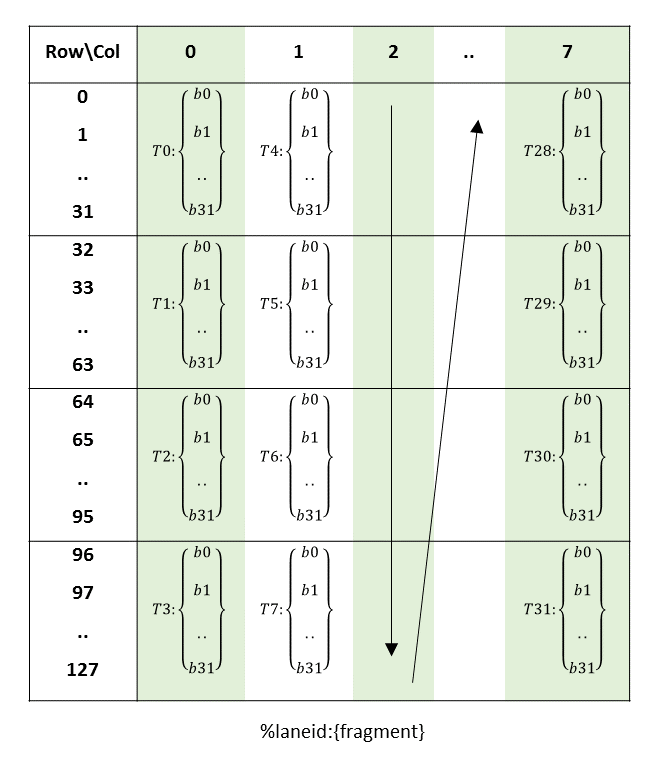

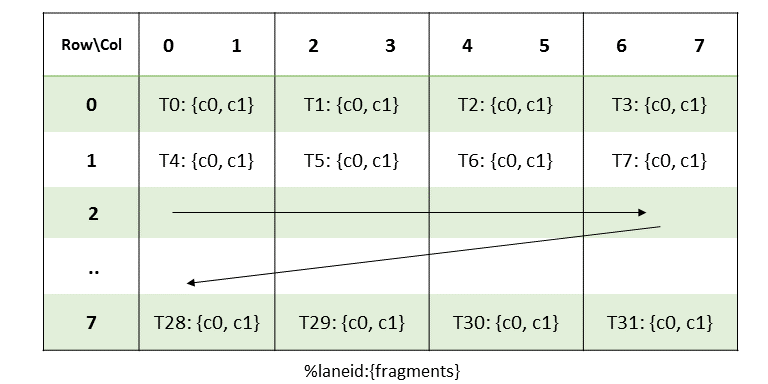

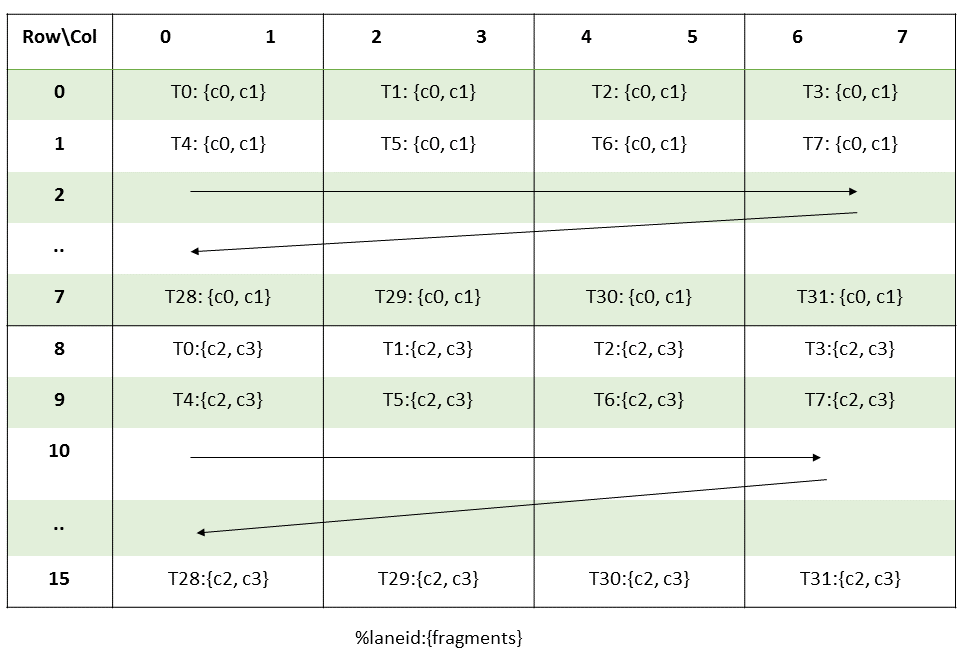

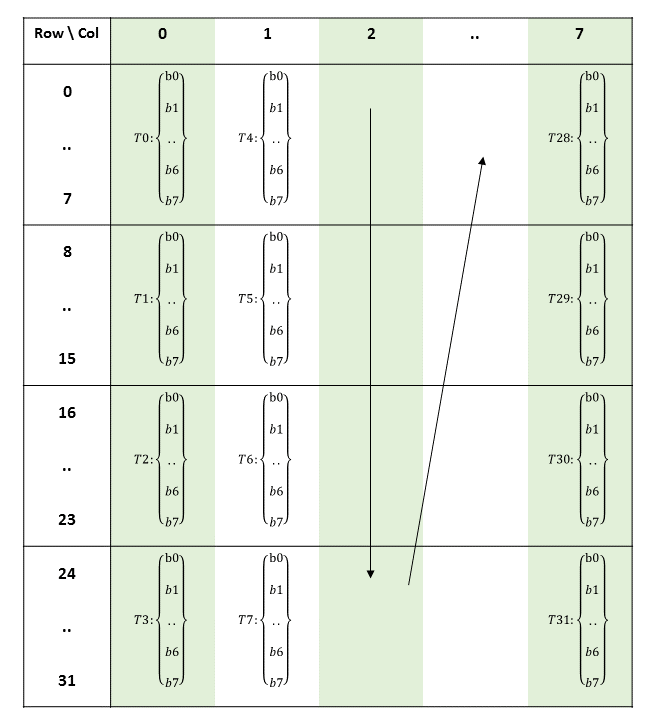

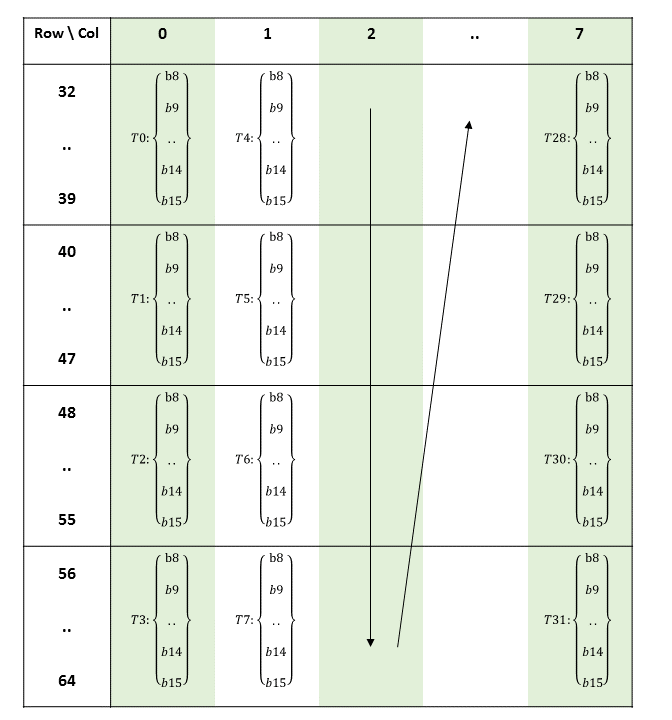

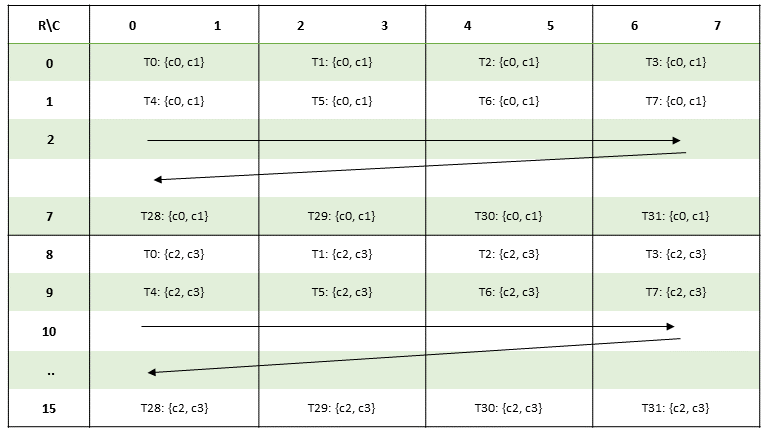

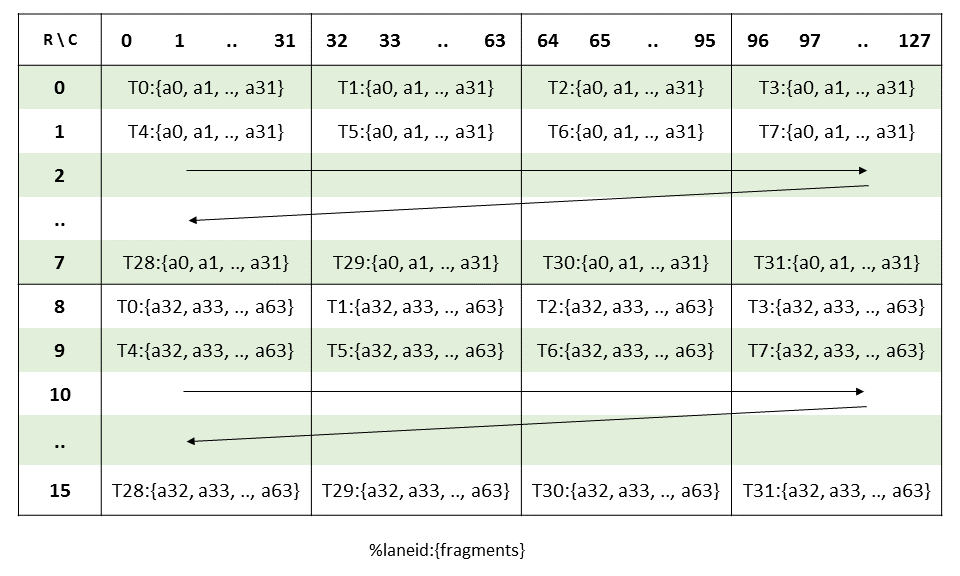

执行内核的线程批次被组织成网格。网格由协作线程阵列或协作线程阵列集群组成,如本节所述并在 图 1 和 图 2 中所示。协作线程阵列 (CTA) 实现 CUDA 线程块,集群实现 CUDA 线程块集群。

2.2.1. 协作线程阵列

并行线程执行 (PTX) 编程模型是显式并行的:PTX 程序指定并行线程阵列的给定线程的执行。协作线程阵列 或 CTA 是一个线程数组,它们并发或并行地执行内核。

CTA 内的线程可以相互通信。为了协调 CTA 内线程的通信,可以指定同步点,线程在这些同步点等待直到 CTA 中的所有线程都到达。

每个线程在 CTA 中都有一个唯一的线程标识符。程序使用数据并行分解来跨 CTA 的线程划分输入、工作和结果。每个 CTA 线程使用其线程标识符来确定其分配的角色、分配特定的输入和输出位置、计算地址以及选择要执行的工作。线程标识符是一个三元素向量 tid(元素为 tid.x、tid.y 和 tid.z),它指定线程在 1D、2D 或 3D CTA 中的位置。每个线程标识符分量的范围从零到该 CTA 维度中的线程 ID 数量。

每个 CTA 都有一个 1D、2D 或 3D 形状,由一个三元素向量 ntid(元素为 ntid.x、ntid.y 和 ntid.z)指定。向量 ntid 指定每个 CTA 维度中的线程数。

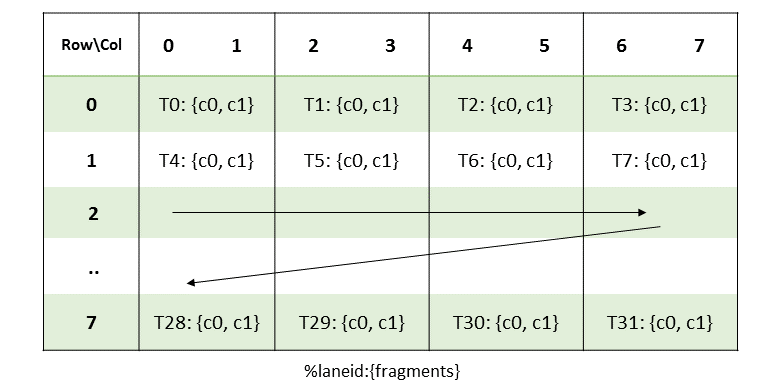

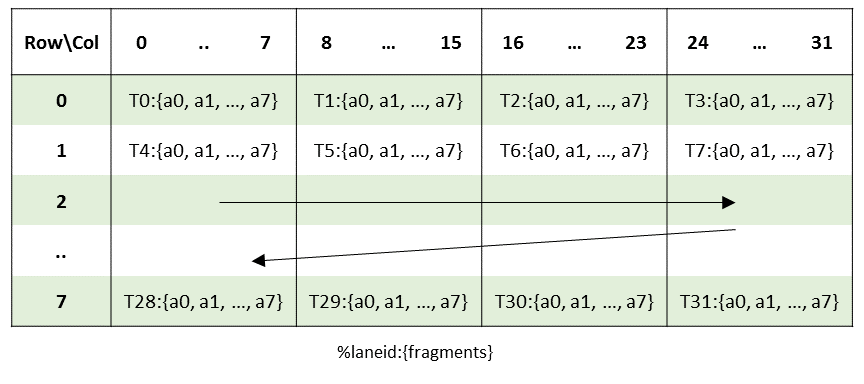

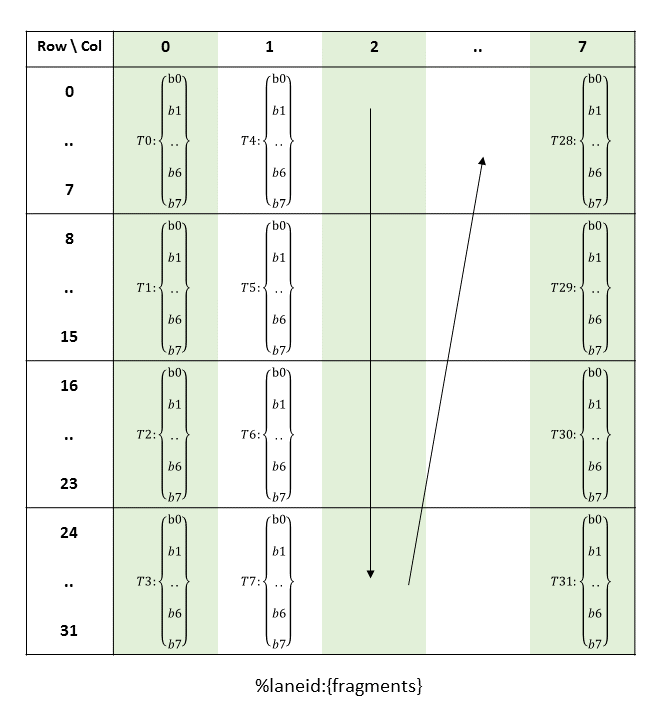

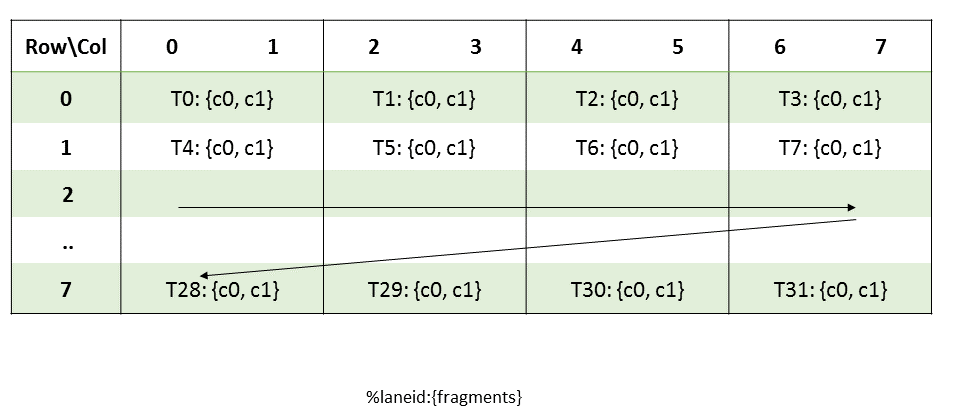

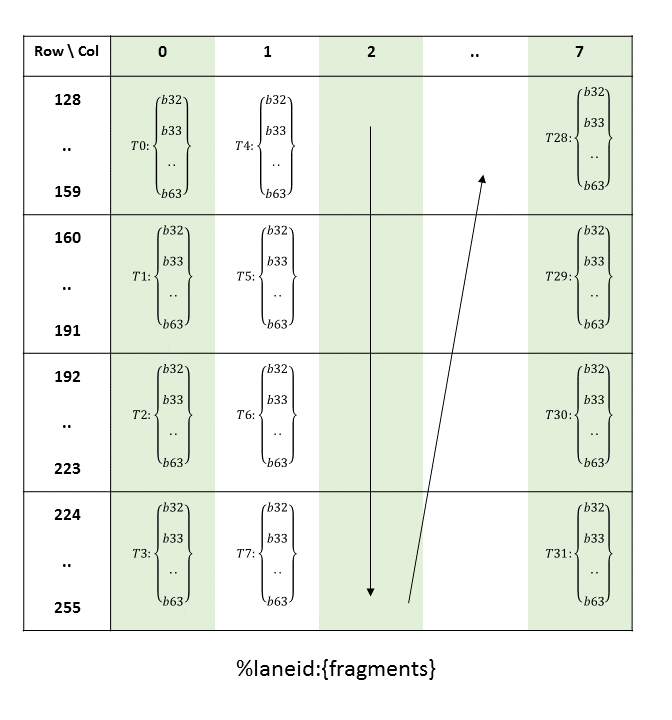

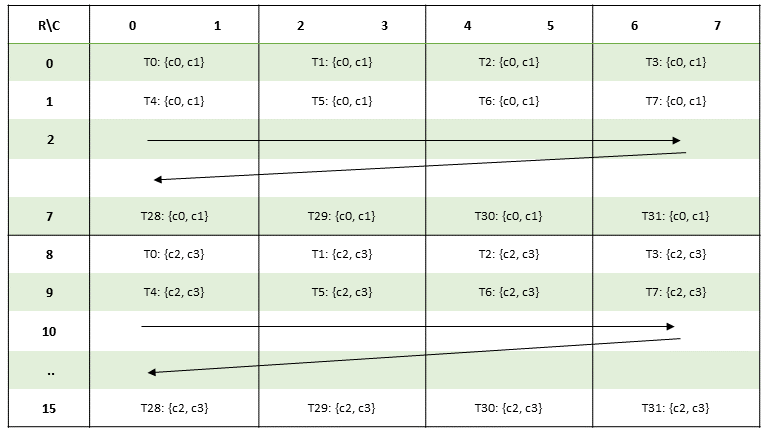

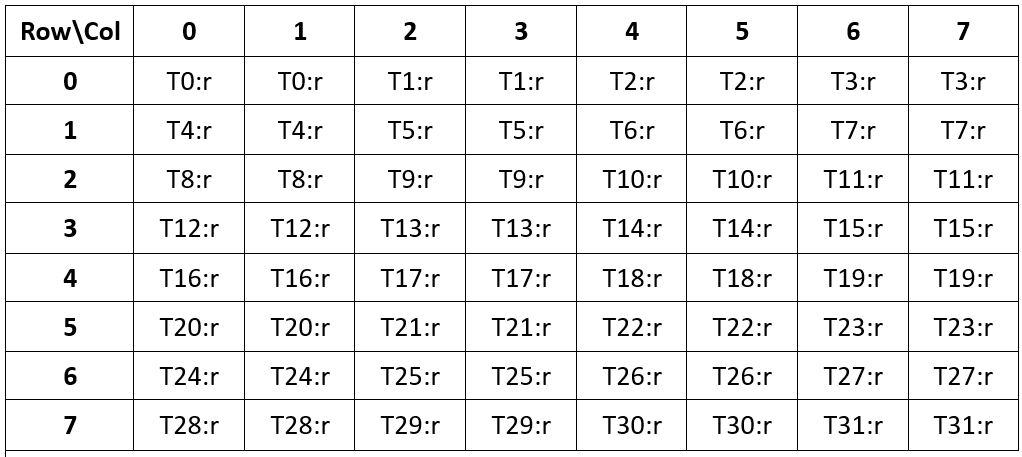

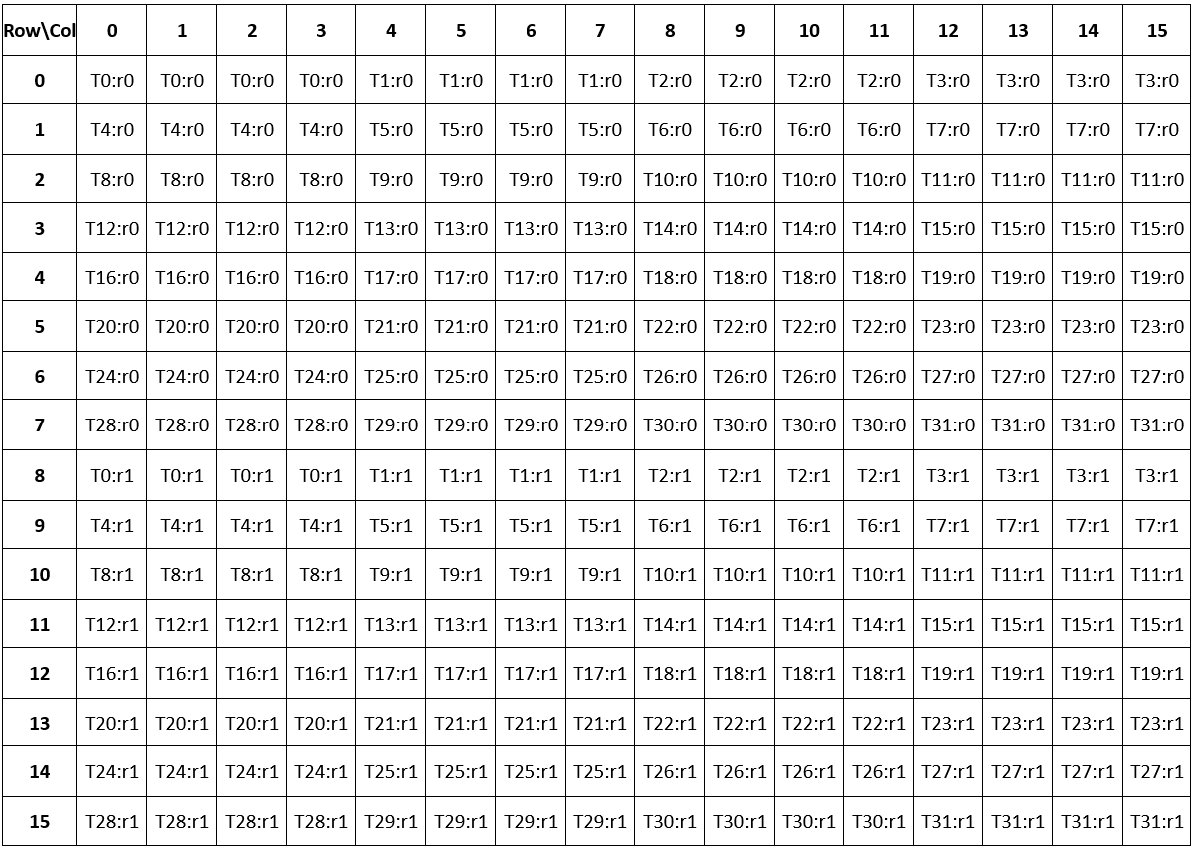

CTA 内的线程以 SIMT(单指令、多线程)方式在称为warp的组中执行。warp 是来自单个 CTA 的线程的最大子集,使得线程同时执行相同的指令。warp 内的线程按顺序编号。warp 大小是机器相关的常数。通常,一个 warp 有 32 个线程。某些应用程序可能能够通过了解 warp 大小来最大化性能,因此 PTX 包括一个运行时立即常量 WARP_SZ,它可以在允许立即操作数的任何指令中使用。

2.2.2. 协作线程阵列集群

集群是一组并发或并行运行的 CTA,可以通过共享内存相互同步和通信。执行 CTA 必须确保对等 CTA 的共享内存存在,然后才能通过共享内存与其通信,并且对等 CTA 在完成共享内存操作之前尚未退出。

集群中不同 CTA 内的线程可以通过共享内存相互同步和通信。集群范围的屏障可用于同步集群内的所有线程。集群中的每个 CTA 在其集群中都有唯一的 CTA 标识符 (cluster_ctaid)。每个 CTA 集群都有由参数 cluster_nctaid 指定的 1D、2D 或 3D 形状。集群中的每个 CTA 在所有维度上也有唯一的 CTA 标识符 (cluster_ctarank)。集群中所有维度上的 CTA 总数由 cluster_nctarank 指定。线程可以通过预定义的只读特殊寄存器 %cluster_ctaid、%cluster_nctaid、%cluster_ctarank、%cluster_nctarank 读取和使用这些值。

集群级别仅适用于目标架构 sm_90 或更高版本。在启动时指定集群级别是可选的。如果用户在启动时指定集群维度,则它将被视为显式集群启动,否则它将被视为默认维度为 1x1x1 的隐式集群启动。PTX 提供了只读特殊寄存器 %is_explicit_cluster 来区分显式和隐式集群启动。

2.2.3. 集群网格

CTA 可以包含的最大线程数和集群可以包含的最大 CTA 数是有限制的。但是,执行相同内核的 CTA 集群可以批量组合成集群网格,以便可以在单个内核调用中启动的线程总数非常大。这样做会降低线程通信和同步,因为不同集群中的线程无法相互通信和同步。

每个集群在集群网格中都有唯一的集群标识符 (clusterid)。每个集群网格都有由参数 nclusterid 指定的 1D、2D 或 3D 形状。每个网格也有唯一的临时网格标识符 (gridid)。线程可以通过预定义的只读特殊寄存器 %tid、%ntid、%clusterid、%nclusterid 和 %gridid 读取和使用这些值。

每个 CTA 在网格中都有唯一的标识符 (ctaid)。每个 CTA 网格都有由参数 nctaid 指定的 1D、2D 或 3D 形状。线程可以使用和读取这些值,通过预定义的只读特殊寄存器 %ctaid 和 %nctaid。

每个内核都作为一批线程执行,这些线程组织成由 CTA 组成的集群网格,其中集群是可选级别,仅适用于目标架构 sm_90 及更高版本。图 1 显示了由 CTA 组成的网格,图 2 显示了由集群组成的网格。

网格可以在彼此之间具有依赖关系的情况下启动——一个网格可以是依赖网格和/或先决条件网格。要了解如何定义网格依赖关系,请参阅 CUDA 编程指南中关于 CUDA Graphs 的章节。

图 1 带有 CTA 的网格

图 2 带有集群的网格

集群是一组协作线程阵列 (CTA),其中 CTA 是一组执行相同内核程序的并发线程。网格是一组由独立执行的 CTA 组成的集群。

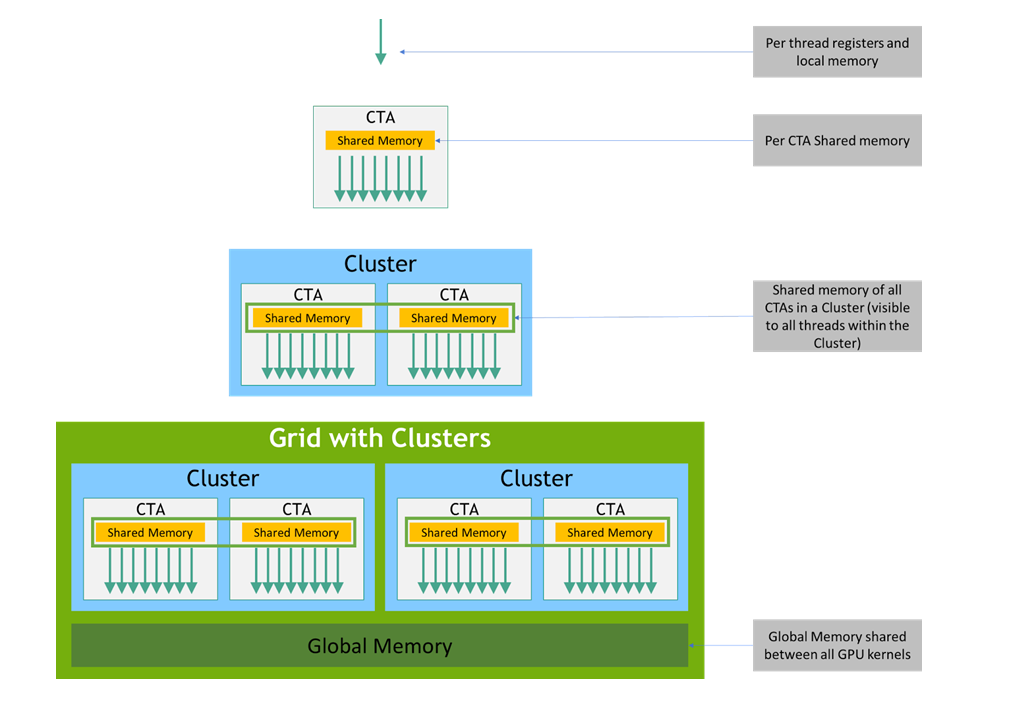

2.3. 内存层次结构

PTX 线程在其执行期间可以访问来自多个状态空间的数据,如 图 3 所示,其中集群级别从目标架构 sm_90 开始引入。每个线程都有一个私有本地内存。每个线程块 (CTA) 都有一个共享内存,该共享内存对块的所有线程以及集群中所有活动块可见,并且具有与块相同的生命周期。最后,所有线程都可以访问相同的全局内存。

还有其他状态空间可供所有线程访问:常量、参数、纹理和表面状态空间。常量和纹理内存是只读的;表面内存是可读写的。全局、常量、参数、纹理和表面状态空间针对不同的内存用途进行了优化。例如,纹理内存为特定数据格式提供不同的寻址模式以及数据过滤。请注意,纹理和表面内存是缓存的,并且在相同的内核调用中,缓存与全局内存写入和表面内存写入不保持一致,因此在同一内核调用中,任何纹理获取或表面读取到已通过全局或表面写入写入的地址都会返回未定义的数据。换句话说,只有当内存位置已被之前的内核调用或内存复制更新时,线程才能安全地读取某些纹理或表面内存位置,但如果它已被同一线程或来自同一内核调用的另一个线程先前更新,则不能安全读取。

全局、常量和纹理状态空间在同一应用程序的内核启动之间是持久存在的。

主机和设备都维护自己的本地内存,分别称为主机内存和设备内存。设备内存可以由主机映射和读取或写入,或者,为了更有效的传输,可以通过优化的 API 调用从主机内存复制,这些 API 调用利用设备的高性能直接内存访问 (DMA) 引擎。

图 3 内存层次结构

3. PTX 机器模型

3.1. 一组 SIMT 多处理器

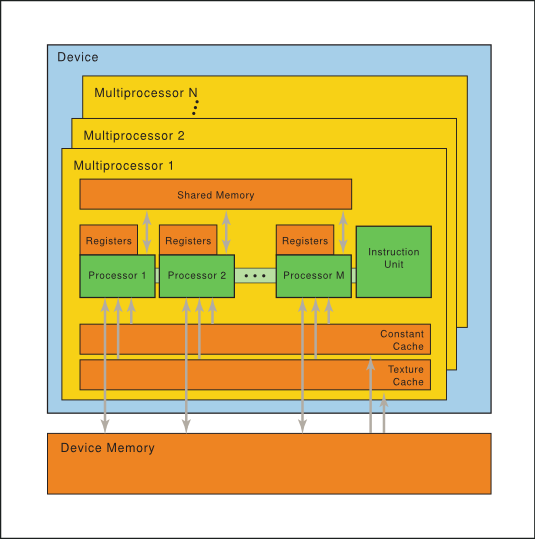

NVIDIA GPU 架构围绕可扩展的多线程流式多处理器 (SM) 阵列构建。当主机程序调用内核网格时,网格的块被枚举并分配给具有可用执行能力的多处理器。线程块的线程在一个多处理器上并发执行。当线程块终止时,新的块在空出的多处理器上启动。

一个多处理器由多个标量处理器 (SP) 核心、一个多线程指令单元和片上共享内存组成。多处理器在硬件中创建、管理和执行并发线程,零调度开销。它实现单指令屏障同步。快速屏障同步以及轻量级线程创建和零开销线程调度有效地支持非常细粒度的并行性,例如,允许通过为每个数据元素(例如图像中的像素、体中的体素、基于网格的计算中的单元)分配一个线程来低粒度分解问题。

为了管理运行多个不同程序的数百个线程,多处理器采用了一种我们称之为 SIMT(单指令、多线程) 的架构。多处理器将每个线程映射到一个标量处理器核心,并且每个标量线程都独立执行,具有自己的指令地址和寄存器状态。多处理器 SIMT 单元创建、管理、调度和执行称为 warp 的并行线程组中的线程。(这个术语起源于编织,第一种并行线程技术。)组成 SIMT warp 的各个线程从相同的程序地址一起启动,但在其他方面可以自由分支和独立执行。

当多处理器被赋予一个或多个线程块来执行时,它会将它们拆分为 warp,这些 warp 由 SIMT 单元调度。将块拆分为 warp 的方式始终相同;每个 warp 包含具有连续递增线程 ID 的线程,第一个 warp 包含线程 0。

在每个指令发出时间,SIMT 单元选择一个准备好执行的 warp,并将下一条指令发给 warp 的活动线程。一个 warp 一次执行一条公共指令,因此当 warp 的所有线程都同意它们的执行路径时,可以实现完全效率。如果 warp 的线程通过数据相关的条件分支发散,则 warp 会串行执行每个分支路径,禁用不在该路径上的线程,并且当所有路径完成时,线程会收敛回相同的执行路径。分支发散仅在 warp 内发生;不同的 warp 独立执行,无论它们是否正在执行公共或不相交的代码路径。

SIMT 架构类似于 SIMD(单指令、多数据)向量组织,因为单条指令控制多个处理元素。一个关键的区别是 SIMD 向量组织向软件公开 SIMD 宽度,而 SIMT 指令指定单个线程的执行和分支行为。与 SIMD 向量机相比,SIMT 使程序员能够为独立的标量线程编写线程级并行代码,以及为协调线程编写数据并行代码。为了正确性,程序员基本上可以忽略 SIMT 行为;但是,通过注意代码很少需要 warp 中的线程发散,可以实现显着的性能提升。实际上,这类似于传统代码中缓存行的作用:在为正确性设计时可以安全地忽略缓存行大小,但在为峰值性能设计时必须在代码结构中考虑缓存行大小。另一方面,向量架构要求软件将加载合并到向量中并手动管理发散。

一个多处理器一次可以处理多少个块取决于给定内核所需的每个线程的寄存器数量和每个块的共享内存量,因为多处理器的寄存器和共享内存在批处理块的所有线程之间分配。如果每个多处理器没有足够的寄存器或共享内存来处理至少一个块,则内核将无法启动。

图 4 硬件模型

一组带有片上共享内存的 SIMT 多处理器。

3.2. 独立线程调度

在 Volta 之前的架构上,warp 使用一个程序计数器,该程序计数器在 warp 中的所有 32 个线程之间共享,以及一个活动掩码,用于指定 warp 的活动线程。因此,来自同一 warp 的线程在发散区域或不同的执行状态下无法相互发出信号或交换数据,并且需要细粒度数据共享的算法(受锁或互斥锁保护)很容易导致死锁,具体取决于争用线程来自哪个 warp。

从 Volta 架构开始,独立线程调度 允许线程之间完全并发,而与 warp 无关。借助独立线程调度,GPU 维护每个线程的执行状态,包括程序计数器和调用堆栈,并且可以在每个线程粒度上产生执行,以便更好地利用执行资源或允许一个线程等待另一个线程生成的数据。调度优化器确定如何将来自同一 warp 的活动线程分组到 SIMT 单元中。这保留了先前 NVIDIA GPU 中的 SIMT 执行的高吞吐量,但具有更大的灵活性:线程现在可以在子 warp 粒度上发散和重新收敛。

如果开发人员对先前硬件架构的 warp 同步性做出假设,则独立线程调度 可能导致参与执行代码的线程集与预期大相径庭。特别是,任何 warp 同步代码(例如,无同步、warp 内缩减)都应重新审视,以确保与 Volta 及更高版本的兼容性。有关更多详细信息,请参阅 Cuda 编程指南 中关于计算能力 7.x 的章节。

4. 语法

PTX 程序是文本源模块(文件)的集合。PTX 源模块具有汇编语言风格的语法,带有指令操作码和操作数。伪操作指定符号和寻址管理。ptxas 优化后端编译器优化和汇编 PTX 源模块以生成相应的二进制目标文件。

4.1. 源格式

源模块是 ASCII 文本。行由换行符 (\n) 分隔。

所有空白字符都是等效的;空白被忽略,除非它用于分隔语言中的标记。

C 预处理器 cpp 可用于处理 PTX 源模块。以 # 开头的行是预处理器指令。以下是常见的预处理器指令

#include、#define、#if、#ifdef、#else、#endif、#line、#file

Harbison 和 Steele 编写的 C: A Reference Manual 提供了对 C 预处理器的良好描述。

PTX 区分大小写,关键字使用小写。

每个 PTX 模块都必须以 .version 指令开始,指定 PTX 语言版本,然后是 .target 指令,指定假定的目标架构。有关这些指令的更多信息,请参阅 PTX 模块指令。

4.3. 语句

PTX 语句是指指令或指令。语句以可选标签开头,以分号结尾。

示例

.reg .b32 r1, r2;

.global .f32 array[N];

start: mov.b32 r1, %tid.x;

shl.b32 r1, r1, 2; // shift thread id by 2 bits

ld.global.b32 r2, array[r1]; // thread[tid] gets array[tid]

add.f32 r2, r2, 0.5; // add 1/2

4.3.1. 指令语句

指令关键字以点开头,因此不可能与用户定义的标识符冲突。PTX 中的指令在 表 1 中列出,并在 状态空间、类型和变量 和 指令 中描述。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.3.2. 指令语句

指令由指令操作码后跟逗号分隔的零个或多个操作数列表组成,并以分号终止。操作数可以是寄存器变量、常量表达式、地址表达式或标签名称。指令有一个可选的保护谓词,用于控制条件执行。保护谓词位于可选标签之后和操作码之前,并写为 @p,其中 p 是谓词寄存器。保护谓词可以是可选的否定,写为 @!p。

目标操作数在前,后跟源操作数。

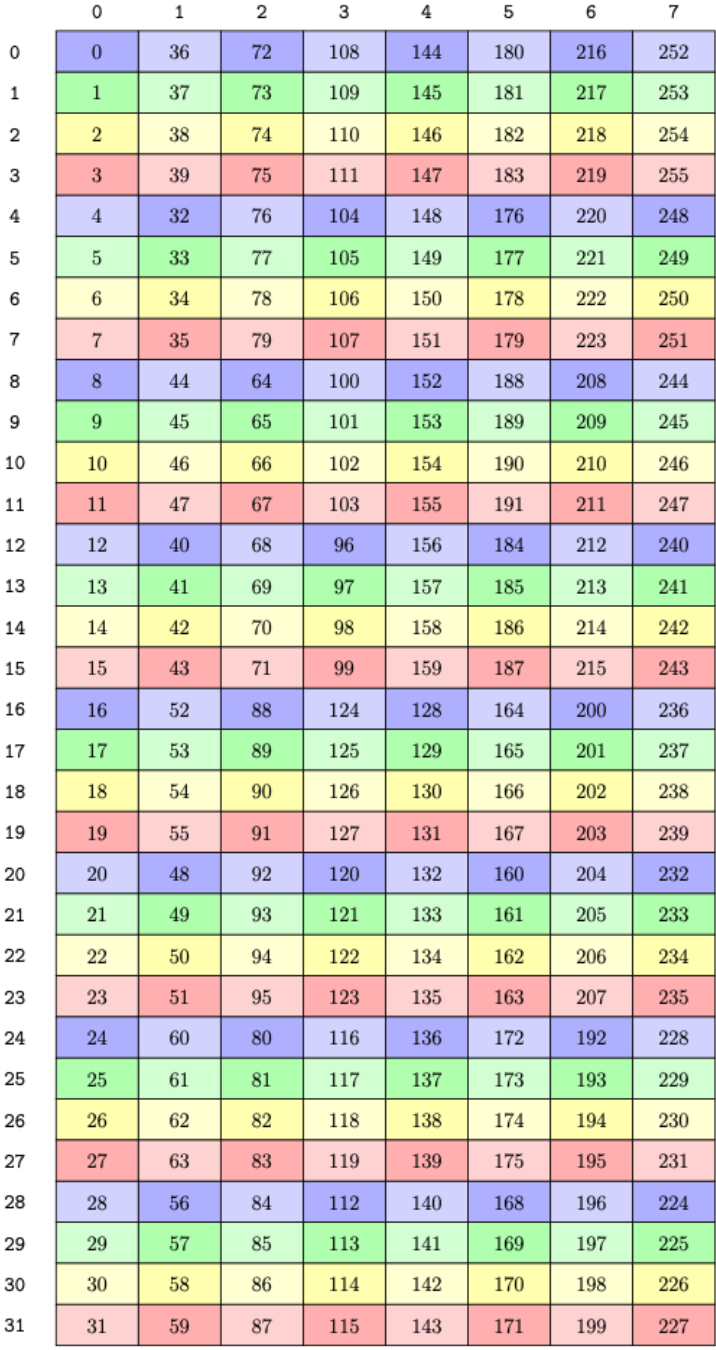

指令关键字在 表 2 中列出。所有指令关键字都是 PTX 中的保留标记。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.4. 标识符

用户自定义的标识符遵循扩展的 C++ 规则:它们要么以字母开头,后跟零个或多个字母、数字、下划线或美元符号;要么以一个下划线、美元符号或百分号开头,后跟一个或多个字母、数字、下划线或美元符号

followsym: [a-zA-Z0-9_$]

identifier: [a-zA-Z]{followsym}* | {[_$%]{followsym}+

PTX 没有指定标识符的最大长度,并建议所有实现都支持至少 1024 个字符的最小长度。

许多高级语言(如 C 和 C++)对于标识符名称都遵循类似的规则,只是不允许使用百分号。PTX 允许百分号作为标识符的第一个字符。百分号可用于避免名称冲突,例如,在用户定义的变量名和编译器生成的名称之间。

PTX 预定义了一个常量和少量以百分号开头的特殊寄存器,列在表 3中。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5. 常量

PTX 支持整数和浮点常量以及常量表达式。这些常量可以用于数据初始化和作为指令的操作数。类型检查规则对于整数、浮点和位大小类型保持不变。对于谓词类型数据和指令,允许使用整数常量,并按照 C 语言中的方式解释,即零值是 False,非零值是 True。

4.5.1. 整数常量

整数常量的大小为 64 位,可以是有符号或无符号的,即,每个整数常量的类型为 .s64 或 .u64。整数常量的有符号/无符号性质是正确评估包含除法和有序比较等操作的常量表达式所必需的,其中操作的行为取决于操作数类型。当在指令或数据初始化中使用时,每个整数常量都将根据其使用时的数据或指令类型转换为适当的大小。

整数文字可以用十进制、十六进制、八进制或二进制表示法书写。语法遵循 C 语言的语法。整数文字可以紧跟字母 U,以指示该文字是无符号的。

hexadecimal literal: 0[xX]{hexdigit}+U?

octal literal: 0{octal digit}+U?

binary literal: 0[bB]{bit}+U?

decimal literal {nonzero-digit}{digit}*U?

整数文字是非负的,其类型由其大小和可选的类型后缀确定,如下所示:文字是有符号的 (.s64),除非该值无法完全用 .s64 表示,或者指定了无符号后缀,在这种情况下,文字是无符号的 (.u64)。

预定义的整数常量 WARP_SZ 指定目标平台上每个 warp 的线程数;迄今为止,所有目标架构的 WARP_SZ 值均为 32。

4.5.2. 浮点常量

浮点常量表示为 64 位双精度值,所有浮点常量表达式都使用 64 位双精度算术进行评估。唯一的例外是用于表示精确单精度浮点值的 32 位十六进制表示法;此类值保留其精确的 32 位单精度值,并且不能用于常量表达式。每个 64 位浮点常量都将根据其使用时的数据或指令类型转换为适当的浮点大小。

浮点文字可以用可选的小数点和可选的有符号指数书写。与 C 和 C++ 不同,没有后缀字母来指定大小;文字始终以 64 位双精度格式表示。

PTX 包括浮点常量的第二种表示形式,用于使用十六进制常量指定精确的机器表示。要指定 IEEE 754 双精度浮点值,常量以 0d 或 0D 开头,后跟 16 个十六进制数字。要指定 IEEE 754 单精度浮点值,常量以 0f 或 0F 开头,后跟 8 个十六进制数字。

0[fF]{hexdigit}{8} // single-precision floating point

0[dD]{hexdigit}{16} // double-precision floating point

例子

mov.f32 $f3, 0F3f800000; // 1.0

4.5.3. 谓词常量

在 PTX 中,整数常量可以用作谓词。对于谓词类型数据初始化器和指令操作数,整数常量按照 C 语言中的方式解释,即零值是 False,非零值是 True。

4.5.4. 常量表达式

在 PTX 中,常量表达式使用与 C 语言中相同的运算符形成,并使用类似于 C 语言中的规则进行评估,但通过限制类型和大小、删除大多数强制转换以及定义完整的语义来简化,以消除 C 语言中表达式评估依赖于实现的情况。

常量表达式由常量文字、一元加号和减号、基本算术运算符(加法、减法、乘法、除法)、比较运算符、条件三元运算符 (?:) 和括号组成。整数常量表达式还允许一元逻辑非 (!)、按位补码 (~)、余数 (%)、移位运算符 (<< 和 >>)、位类型运算符 (&、| 和 ^) 和逻辑运算符 (&&、||)。

PTX 中的常量表达式不支持整数和浮点之间的强制转换。

常量表达式使用与 C 语言中相同的运算符优先级进行评估。表 4 给出了运算符优先级和结合性。一元运算符的运算符优先级最高,并且在图表中每行递减。同一行上的运算符具有相同的优先级,并且对于一元运算符从右到左评估,对于二元运算符从左到右评估。

类型 |

运算符符号 |

运算符名称 |

结合性 |

|---|---|---|---|

初等 |

|

括号 |

不适用 |

一元 |

|

加号、减号、取反、补码 |

右 |

|

强制转换 |

右 |

|

二元 |

|

乘法、除法、余数 |

左 |

|

加法、减法 |

||

|

移位 |

||

|

有序比较 |

||

|

等于、不等于 |

||

|

按位与 |

||

|

按位异或 |

||

|

按位或 |

||

|

逻辑与 |

||

|

逻辑或 |

||

三元 |

|

条件 |

右 |

4.5.5. 整数常量表达式求值

整数常量表达式在编译时根据一组规则进行评估,这些规则确定每个子表达式的类型(有符号 .s64 与无符号 .u64)。这些规则基于 C 语言中的规则,但它们已简化为仅适用于 64 位整数,并且在所有情况下都完全定义了行为(特别是对于余数和移位运算符)。

-

文字是有符号的,除非需要无符号以防止溢出,或者除非文字使用

U后缀。例如42、0x1234、0123是有符号的。0xfabc123400000000、42U、0x1234U是无符号的。

-

一元加号和减号保留输入操作数的类型。例如

+123、-1、-(-42)是有符号的。-1U、-0xfabc123400000000是无符号的。

一元逻辑非 (

!) 产生一个有符号的结果,值为0或1。一元按位补码 (

~) 将源操作数解释为无符号,并产生一个无符号的结果。某些二元运算符需要对源操作数进行规范化。这种规范化称为常用算术转换,如果任一操作数是无符号的,则只需将两个操作数都转换为无符号类型。

加法、减法、乘法和除法执行常用算术转换,并产生与转换后的操作数类型相同的结果。也就是说,如果任一源操作数是无符号的,则操作数和结果是无符号的,否则是有符号的。

余数 (

%) 将操作数解释为无符号。请注意,这与 C 语言不同,C 语言允许负除数,但将行为定义为依赖于实现。左移和右移将第二个操作数解释为无符号,并产生与第一个操作数类型相同的结果。请注意,右移的行为由第一个操作数的类型决定:有符号值的右移是算术移位并保留符号,而无符号值的右移是逻辑移位并移入零位。

与 (

&)、或 (|) 和异或 (^) 执行常用算术转换,并产生与转换后的操作数类型相同的结果。逻辑与 (

&&)、逻辑或 (||)、等于 (==) 和不等于 (!=) 产生一个有符号的结果。结果值为 0 或 1。有序比较 (

<、<=、>、>=) 对源操作数执行常用算术转换,并产生一个有符号的结果。结果值为0或1。使用 (

.s64) 和 (.u64) 强制转换支持将表达式强制转换为有符号或无符号。对于条件运算符 (

? :),第一个操作数必须是整数,第二个和第三个操作数要么都是整数,要么都是浮点数。对第二个和第三个操作数执行常用算术转换,结果类型与转换后的类型相同。

4.5.6. 常量表达式求值规则摘要

表 5 包含常量表达式求值规则的摘要。

类型 |

运算符 |

操作数类型 |

操作数解释 |

结果类型 |

|---|---|---|---|---|

初等 |

|

任何类型 |

与源相同 |

与源相同 |

常量文字 |

不适用 |

不适用 |

|

|

一元 |

|

任何类型 |

与源相同 |

与源相同 |

|

整数 |

零或非零 |

|

|

|

整数 |

|

|

|

强制转换 |

|

整数 |

|

|

|

整数 |

|

|

|

二元 |

|

|

|

|

整数 |

使用常用转换 |

转换后的类型 |

||

|

|

|

|

|

整数 |

使用常用转换 |

|

||

|

|

|

|

|

整数 |

使用常用转换 |

|

||

|

整数 |

|

|

|

|

整数 |

第一个不变,第二个是 |

与第一个操作数相同 |

|

|

整数 |

|

|

|

|

整数 |

零或非零 |

|

|

三元 |

|

|

与源相同 |

|

|

使用常用转换 |

转换后的类型 |

5. 状态空间、类型和变量

虽然给定目标 GPU 中可用的特定资源会有所不同,但资源类型在不同平台之间是通用的,并且这些资源在 PTX 中通过状态空间和数据类型进行抽象。

5.1. 状态空间

状态空间是具有特定特征的存储区域。所有变量都驻留在某个状态空间中。状态空间的特征包括其大小、可寻址性、访问速度、访问权限以及线程之间的共享级别。

PTX 中定义的状态空间是并行编程和图形编程的副产品。状态空间列表如表 6所示,状态空间的属性如表 7所示。

名称 |

描述 |

|---|---|

|

寄存器,快速。 |

|

特殊寄存器。只读;预定义;平台特定。 |

|

共享,只读内存。 |

|

全局内存,由所有线程共享。 |

|

本地内存,每个线程私有。 |

|

内核参数,每个网格定义;或 函数或局部参数,每个线程定义。 |

|

可寻址内存,每个 CTA 定义,在定义它的 CTA 的整个生命周期内可供集群中的所有线程访问。 |

|

全局纹理内存(已弃用)。 |

名称 |

可寻址 |

可初始化 |

访问 |

共享 |

|---|---|---|---|---|

|

否 |

否 |

R/W |

每个线程 |

|

否 |

否 |

RO |

每个 CTA |

|

是 |

是1 |

RO |

每个网格 |

|

是 |

是1 |

R/W |

上下文 |

|

是 |

否 |

R/W |

每个线程 |

|

是2 |

否 |

RO |

每个网格 |

|

受限3 |

否 |

R/W |

每个线程 |

|

是 |

否 |

R/W |

每个集群5 |

|

否4 |

是,通过驱动程序 |

RO |

上下文 |

|

注释 1 2 仅可通过 3 可通过 4 仅可通过 5 对拥有 CTA 和集群中的其他活动 CTA 可见。 |

||||

5.1.1. 寄存器状态空间

寄存器(.reg 状态空间)是快速存储位置。寄存器的数量有限,并且会因平台而异。当超出限制时,寄存器变量将被溢出到内存中,从而导致性能变化。对于每个架构,都有建议的最大寄存器使用数量(有关详细信息,请参阅CUDA 编程指南)。

寄存器可以是类型化的(有符号整数、无符号整数、浮点数、谓词)或无类型的。寄存器大小受到限制;除了 1 位谓词寄存器外,标量寄存器的宽度为 8 位、16 位、32 位、64 位或 128 位,向量寄存器的宽度为 16 位、32 位、64 位或 128 位。8 位寄存器最常见的用途是与 ld、st 和 cvt 指令一起使用,或作为向量元组的元素。

寄存器与其他状态空间的不同之处在于它们不是完全可寻址的,即,不可能引用寄存器的地址。当编译为使用应用程序二进制接口 (ABI) 时,寄存器变量仅限于函数作用域,并且不能在模块作用域中声明。当编译包含模块作用域 .reg 变量的旧版 PTX 代码(ISA 版本早于 3.0)时,编译器会静默禁用 ABI 的使用。寄存器可能具有多字加载和存储所需的对齐边界。

5.1.2. 特殊寄存器状态空间

特殊寄存器 (.sreg) 状态空间保存预定义的、平台特定的寄存器,例如网格、集群、CTA 和线程参数、时钟计数器和性能监控寄存器。所有特殊寄存器都是预定义的。

5.1.3. 常量状态空间

常量 (.const) 状态空间是由主机初始化的只读内存。常量内存通过 ld.const 指令访问。常量内存的大小受到限制,目前限制为 64 KB,可用于保存静态大小的常量变量。还有额外的 640 KB 常量内存,组织为十个独立的 64 KB 区域。驱动程序可以在这些区域中分配和初始化常量缓冲区,并将指向缓冲区的指针作为内核函数参数传递。由于这十个区域不是连续的,因此驱动程序必须确保常量缓冲区的分配方式是每个缓冲区都完全适合 64 KB 区域内,并且不会跨越区域边界。

静态大小的常量变量具有可选的变量初始化器;没有显式初始化器的常量变量默认初始化为零。由驱动程序分配的常量缓冲区由主机初始化,指向此类缓冲区的指针作为参数传递给内核。有关将指向常量缓冲区的指针作为内核参数传递的更多详细信息,请参阅内核函数参数属性的描述。

5.1.3.1. 分块常量状态空间(已弃用)

以前版本的 PTX 将常量内存公开为一组 11 个 64 KB 块,变量声明和访问期间需要显式块号。

在 PTX ISA 2.2 版本之前,常量内存被组织成固定大小的块。有 11 个 64 KB 的块,块使用 .const[bank] 修饰符指定,其中 bank 的范围从 0 到 10。如果未给出块号,则假定为零号块。

按照惯例,零号块用于所有静态大小的常量变量。其余块用于声明不完整的常量数组(例如在 C 语言中),其中大小在编译时未知。例如,声明

.extern .const[2] .b32 const_buffer[];

导致 const_buffer 指向常量块二的开头。然后,此指针可用于访问整个 64 KB 常量块。在同一块中声明的多个不完整数组变量被别名化,每个变量都指向指定常量块的起始地址。

要访问常量块 1 到 10 中的数据,加载指令的状态空间中需要块号。例如,块 2 中的不完整数组按如下方式访问

.extern .const[2] .b32 const_buffer[];

ld.const[2].b32 %r1, [const_buffer+4]; // load second word

在 PTX ISA 2.2 版本中,我们取消了显式块,并将驱动程序分配的常量缓冲区的不完整数组表示形式替换为内核参数属性,该属性允许将指向常量缓冲区的指针作为内核参数传递。

5.1.4. 全局状态空间

全局 (.global) 状态空间是上下文中所有线程都可以访问的内存。它是不同 CTA、集群和网格中的线程可以通信的机制。使用 ld.global、st.global 和 atom.global 访问全局变量。

全局变量具有可选的变量初始化器;没有显式初始化器的全局变量默认初始化为零。

5.1.5. 本地状态空间

本地状态空间 (.local) 是每个线程用于保存其自身数据的私有内存。它通常是带有缓存的标准内存。大小受到限制,因为它必须按每个线程进行分配。使用 ld.local 和 st.local 访问本地变量。

当编译为使用应用程序二进制接口 (ABI) 时,.local 状态空间变量必须在函数作用域内声明,并在堆栈上分配。在不支持堆栈的实现中,所有本地内存变量都存储在固定地址,不支持递归函数调用,并且 .local 变量可以在模块作用域中声明。当编译包含模块作用域 .local 变量的旧版 PTX 代码(ISA 版本早于 3.0)时,编译器会静默禁用 ABI 的使用。

5.1.6. 参数状态空间

参数 (.param) 状态空间用于 (1) 将输入参数从主机传递到内核,(2a) 声明从内核执行内部调用的设备函数的形式输入和返回参数,以及 (2b) 声明本地作用域的字节数组变量,这些变量充当函数调用参数,通常用于按值将大型结构体传递给函数。内核函数参数与设备函数参数在访问和共享方面有所不同(只读与读写,每个内核与每个线程)。请注意,PTX ISA 1.x 版本仅支持 .param 空间中的内核函数参数;设备函数参数以前仅限于寄存器状态空间。在 PTX ISA 2.0 版本中引入了将参数状态空间用于设备函数参数,并且需要目标架构 sm_20 或更高版本。可以在具有 .param 状态空间的指令上指定附加的子限定符 ::entry 或 ::func,以指示地址是指内核函数参数还是设备函数参数。如果在 .param 状态空间中未指定子限定符,则默认子限定符特定于且依赖于确切的指令。例如,st.param 等效于 st.param::func,而 isspacep.param 等效于 isspacep.param::entry。有关默认子限定符假设的更多详细信息,请参阅指令描述。

注意

参数空间的位置是特定于实现的。例如,在某些实现中,内核参数驻留在全局内存中。在这种情况下,参数空间和全局空间之间不提供访问保护。尽管内核参数空间的精确定位是特定于实现的,但内核参数空间窗口始终包含在全局空间窗口内。同样,函数参数根据应用程序二进制接口 (ABI) 的函数调用约定映射到参数传递寄存器和/或堆栈位置。因此,PTX 代码不应对 .param 空间变量的相对位置或顺序做出任何假设。

5.1.6.1. 内核函数参数

每个内核函数定义都包含一个可选的参数列表。这些参数是在 .param 状态空间中声明的可寻址只读变量。从主机传递到内核的值通过使用 ld.param 指令的这些参数变量访问。内核参数变量在来自网格内所有集群的所有 CTA 之间共享。

内核参数的地址可以使用 mov 指令移动到寄存器中。结果地址位于 .param 状态空间中,并使用 ld.param 指令访问。

例子

.entry foo ( .param .b32 N, .param .align 8 .b8 buffer[64] )

{

.reg .u32 %n;

.reg .f64 %d;

ld.param.u32 %n, [N];

ld.param.f64 %d, [buffer];

...

例子

.entry bar ( .param .b32 len )

{

.reg .u32 %ptr, %n;

mov.u32 %ptr, len;

ld.param.u32 %n, [%ptr];

...

内核函数参数可以表示普通数据值,或者它们可以保存指向常量、全局、本地或共享状态空间中对象的地址。对于指针的情况,编译器和运行时系统需要知道哪些参数是指针,以及它们指向哪个状态空间。内核参数属性指令用于在 PTX 级别提供此信息。有关内核参数属性指令的描述,请参阅内核函数参数属性。

注意

当前的实现在程序中不允许创建指向常量变量的通用指针 (cvta.const),如果程序将指向常量缓冲区的指针作为内核参数传递。

5.1.6.2. 内核函数参数属性

内核函数参数可以使用可选的 .ptr 属性声明,以指示参数是指向内存的指针,并指示所指向内存的状态空间和对齐方式。内核参数属性:.ptr 描述了 .ptr 内核参数属性。

5.1.6.3. 内核参数属性:.ptr

.ptr

内核参数对齐属性。

语法

.param .type .ptr .space .align N varname

.param .type .ptr .align N varname

.space = { .const, .global, .local, .shared };

描述

用于指定指针类型内核参数指向的内存的状态空间,以及可选的对齐方式。对齐值 N(如果存在)必须是 2 的幂。如果未指定状态空间,则该指针被假定为指向常量、全局、本地或共享内存之一的通用地址。如果未指定对齐方式,则假定所指向的内存按 4 字节边界对齐。

.ptr、.space 和 .align 之间的空格可以省略以提高可读性。

PTX ISA 注释

在 PTX ISA 版本 2.2 中引入。

在 PTX ISA 版本 3.1 中添加了对 .const 空间的通用寻址的支持。

目标 ISA 注释

所有目标架构均支持。

示例

.entry foo ( .param .u32 param1,

.param .u32 .ptr.global.align 16 param2,

.param .u32 .ptr.const.align 8 param3,

.param .u32 .ptr.align 16 param4 // generic address

// pointer

) { .. }

5.1.6.4. 设备函数参数

PTX ISA 版本 2.0 将参数空间的使用扩展到设备函数参数。最常见的用途是通过值传递不适合 PTX 寄存器的对象,例如大于 8 字节的 C 结构体。在这种情况下,将使用参数空间中的字节数组。通常,调用者将声明一个局部作用域的 .param 字节数组变量,该变量表示扁平化的 C 结构体或联合。这将通过值传递给被调用者,被调用者声明一个 .param 形式参数,该参数具有与传递的参数相同的大小和对齐方式。

例子

// pass object of type struct { double d; int y; };

.func foo ( .reg .b32 N, .param .align 8 .b8 buffer[12] )

{

.reg .f64 %d;

.reg .s32 %y;

ld.param.f64 %d, [buffer];

ld.param.s32 %y, [buffer+8];

...

}

// code snippet from the caller

// struct { double d; int y; } mystruct; is flattened, passed to foo

...

.reg .f64 dbl;

.reg .s32 x;

.param .align 8 .b8 mystruct;

...

st.param.f64 [mystruct+0], dbl;

st.param.s32 [mystruct+8], x;

call foo, (4, mystruct);

...

有关更多详细信息,请参阅关于函数调用语法的章节。

函数输入参数可以通过 ld.param 读取,函数返回参数可以使用 st.param 写入;写入输入参数或从返回参数读取是非法的。

除了通过值传递结构体之外,每当在被调用函数内部获取形式参数的地址时,也需要 .param 空间。在 PTX 中,可以使用 mov 指令将函数输入参数的地址移动到寄存器中。请注意,如有必要,参数将被复制到堆栈,因此地址将位于 .local 状态空间中,并通过 ld.local 和 st.local 指令访问。无法使用 mov 获取局部作用域的 .param 空间变量的地址。从 PTX ISA 版本 6.0 开始,可以使用 mov 指令获取设备函数返回参数的地址。

例子

// pass array of up to eight floating-point values in buffer

.func foo ( .param .b32 N, .param .b32 buffer[32] )

{

.reg .u32 %n, %r;

.reg .f32 %f;

.reg .pred %p;

ld.param.u32 %n, [N];

mov.u32 %r, buffer; // forces buffer to .local state space

Loop:

setp.eq.u32 %p, %n, 0;

@%p bra Done;

ld.local.f32 %f, [%r];

...

add.u32 %r, %r, 4;

sub.u32 %n, %n, 1;

bra Loop;

Done:

...

}

5.1.8. 纹理状态空间(已弃用)

纹理 (.tex) 状态空间是通过纹理指令访问的全局内存。它由上下文中的所有线程共享。纹理内存是只读且缓存的,因此对纹理内存的访问与全局内存存储到纹理图像不一致。

GPU 硬件具有固定数量的纹理绑定,可以在单个内核中访问(通常为 128 个)。.tex 指令会将命名的纹理内存变量绑定到硬件纹理标识符,其中纹理标识符从零开始按顺序分配。可以将多个名称绑定到同一个物理纹理标识符。如果超出物理资源的最大数量,则会生成错误。纹理名称的类型必须为 .u32 或 .u64。

物理纹理资源是按内核粒度分配的,并且 .tex 变量需要在全局作用域中定义。

纹理内存是只读的。纹理的基地址假定按 16 字节边界对齐。

例子

.tex .u32 tex_a; // bound to physical texture 0

.tex .u32 tex_c, tex_d; // both bound to physical texture 1

.tex .u32 tex_d; // bound to physical texture 2

.tex .u32 tex_f; // bound to physical texture 3

注意

显式声明纹理状态空间中的变量已被弃用,程序应改为通过 .texref 类型的变量引用纹理内存。.tex 指令被保留以实现向后兼容性,并且在 .tex 状态空间中声明的变量等同于 .global 状态空间中模块作用域的 .texref 变量。

例如,传统的 PTX 定义,例如

.tex .u32 tex_a;

等同于

.global .texref tex_a;

有关 .texref 类型的描述,请参阅纹理采样器和表面类型,有关其在纹理指令中的使用,请参阅纹理指令。

5.2. 类型

5.2.1. 基本类型

在 PTX 中,基本类型反映了目标架构支持的本机数据类型。基本类型指定了基本类型和大小。寄存器变量始终是基本类型,指令对这些类型进行操作。相同的类型大小说明符用于变量定义和类型指令,因此它们的名称有意缩短。

表 8 列出了每种基本类型的基本类型说明符

基本类型 |

基本类型说明符 |

|---|---|

有符号整数 |

|

无符号整数 |

|

浮点数 |

|

位(无类型) |

|

谓词 |

|

大多数指令具有一个或多个类型说明符,需要这些说明符才能完全指定指令行为。操作数类型和大小会根据指令类型进行兼容性检查。

如果两个基本类型具有相同的基本类型并且大小相同,则它们是兼容的。如果有符号和无符号整数类型的大小相同,则它们是兼容的。位大小类型与任何大小相同的基本类型兼容。

原则上,所有变量(谓词除外)都可以仅使用位大小类型声明,但类型化变量可以提高程序的可读性,并允许更好的操作数类型检查。

5.2.2. 子字大小的限制使用

.u8、.s8 和 .b8 指令类型仅限于 ld、st 和 cvt 指令。.f16 浮点类型仅允许在与 .f32、.f64 类型之间的转换、半精度浮点指令和纹理提取指令中使用。.f16x2 浮点类型仅允许在半精度浮点算术指令和纹理提取指令中使用。

为方便起见,ld、st 和 cvt 指令允许源和目标数据操作数比指令类型大小更宽,以便可以使用常规宽度寄存器加载、存储和转换窄值。例如,在加载、存储或转换为其他类型和大小的值时,8 位或 16 位的值可以直接保存在 32 位或 64 位寄存器中。

5.2.3. 备用浮点数据格式

PTX 中支持的基本浮点类型具有隐式的位表示形式,指示用于存储指数和尾数的位数。例如,.f16 类型表示为指数保留 5 位,为尾数保留 10 位。除了基本类型假定的浮点表示形式之外,PTX 还允许以下备用浮点数据格式

-

bf16数据格式 -

此数据格式是一种 16 位浮点格式,其中指数为 8 位,尾数为 7 位。包含

bf16数据的寄存器变量必须使用.b16类型声明。 -

e4m3数据格式 -

此数据格式是一种 8 位浮点格式,其中指数为 4 位,尾数为 3 位。

e4m3编码不支持无穷大,并且NaN值限制为0x7f和0xff。包含e4m3值的寄存器变量必须使用位大小类型声明。 -

e5m2数据格式 -

此数据格式是一种 8 位浮点格式,其中指数为 5 位,尾数为 2 位。包含

e5m2值的寄存器变量必须使用位大小类型声明。 -

tf32数据格式 -

此数据格式是一种特殊的 32 位浮点格式,受矩阵乘法累加指令支持,其范围与

.f32相同,但精度降低(>=10 位)。tf32格式的内部布局是实现定义的。PTX 方便了从单精度.f32类型到tf32格式的转换。包含tf32数据的寄存器变量必须使用.b32类型声明。 -

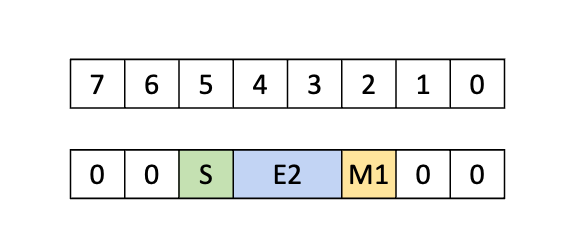

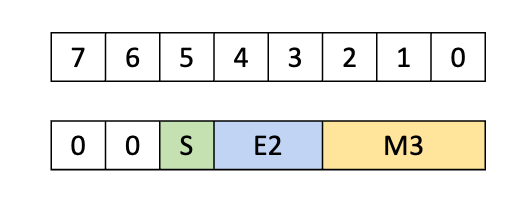

e2m1数据格式 -

此数据格式是一种 4 位浮点格式,其中指数为 2 位,尾数为 1 位。

e2m1编码不支持无穷大和NaN。e2m1值必须以打包格式使用,指定为e2m1x2。包含两个e2m1值的寄存器变量必须使用.b8类型声明。 -

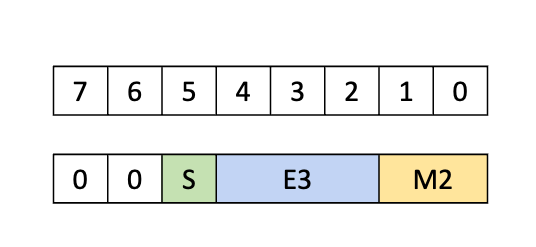

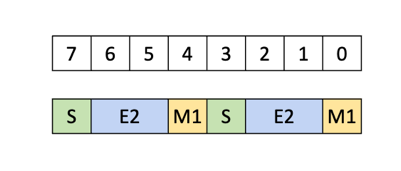

e2m3数据格式 -

此数据格式是一种 6 位浮点格式,其中指数为 2 位,尾数为 3 位。

e2m3编码不支持无穷大和NaN。e2m3值必须以打包格式使用,指定为e2m3x2。包含两个e2m3值的寄存器变量必须使用.b16类型声明,其中每个.b8元素都具有 6 位浮点值,并且 2 个 MSB 位用零填充。 -

e3m2数据格式 -

此数据格式是一种 6 位浮点格式,其中指数为 3 位,尾数为 2 位。

e3m2编码不支持无穷大和NaN。e3m2值必须以打包格式使用,指定为e3m2x2。包含两个e3m2值的寄存器变量必须使用.b16类型声明,其中每个.b8元素都具有 6 位浮点值,并且 2 个 MSB 位用零填充。 -

ue8m0数据格式 -

此数据格式是一种 8 位无符号浮点格式,其中指数为 8 位,尾数为 0 位。

ue8m0编码不支持无穷大。NaN值限制为0xff。ue8m0值必须以打包格式使用,指定为ue8m0x2。包含两个ue8m0值的寄存器变量必须使用.b16类型声明。 -

ue4m3数据格式 -

此数据格式是一种 7 位无符号浮点格式,其中指数为 4 位,尾数为 3 位。

ue4m3编码不支持无穷大。NaN值限制为0x7f。包含单个ue4m3值的寄存器变量必须使用.b8类型声明,其中 MSB 位用零填充。

备用数据格式不能用作基本类型。它们作为某些指令的源或目标格式受支持。

5.2.4. 打包数据类型

某些 PTX 指令并行地对两组或多组输入进行操作,并产生两个或多个输出。此类指令可以使用以打包格式存储的数据。PTX 支持将两个或四个相同标量数据类型的值打包成一个更大的值。打包值被视为打包数据类型的值。在本节中,我们将描述 PTX 中支持的打包数据类型。

5.2.4.1. 打包浮点数据类型

PTX 支持各种打包浮点数据类型变体。其中,只有 .f16x2 作为基本类型受支持,而其他类型不能用作基本类型 - 它们作为某些指令的指令类型受支持。当使用具有此类非基本类型的指令时,操作数数据变量必须是适当大小的位类型。例如,对于指令类型为 .bf16x2 的指令,所有操作数变量都必须是 .b32 类型。表 9 描述了 PTX 中各种打包浮点数据类型变体。

打包浮点类型 |

打包格式中包含的元素数量 |

每个元素的类型 |

声明中要使用的寄存器变量类型 |

|---|---|---|---|

|

两个 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

||

|

|

||

|

|

||

|

|

|

|

|

四个 |

|

|

|

|

||

|

|

||

|

|

||

|

|

5.2.4.2. 打包整数数据类型

PTX 支持两种打包整数数据类型变体:.u16x2 和 .s16x2。打包数据类型由两个 .u16 或 .s16 值组成。包含 .u16x2 或 .s16x2 数据的寄存器变量必须使用 .b32 类型声明。打包整数数据类型不能用作基本类型。它们作为某些指令的指令类型受支持。

5.3. 纹理采样器和表面类型

PTX 包括内置的不透明类型,用于定义纹理、采样器和表面描述符变量。这些类型具有类似于结构的命名字段,但 PTX 程序隐藏了有关布局、字段顺序、基地址和整体大小的所有信息,因此称为不透明。这些不透明类型的使用仅限于

全局(模块)作用域内和内核入口参数列表中的变量定义。

使用逗号分隔的静态赋值表达式对类型的命名成员进行模块作用域变量的静态初始化。

通过纹理和表面加载/存储指令 (

tex、suld、sust、sured) 引用纹理、采样器或表面。通过查询指令 (

txq、suq) 检索命名成员的值。使用

mov创建指向不透明变量的指针,例如,mov.u64 reg, opaque_var;。生成的指针可以存储到内存和从内存加载,作为参数传递给函数,并通过纹理和表面加载、存储和查询指令取消引用,但该指针不能以其他方式视为地址,即,使用ld和st指令访问指针,或执行指针运算将导致未定义的行为。不透明变量不能出现在初始化列表中,例如,初始化指向不透明变量的指针。

注意

从 PTX ISA 版本 3.1 开始支持使用指向不透明变量的指针间接访问纹理和表面,并且需要目标 sm_20 或更高版本。

仅在统一纹理模式下支持对纹理的间接访问(见下文)。

三个内置类型是 .texref、.samplerref 和 .surfref。为了使用纹理和采样器,PTX 有两种操作模式。在统一模式下,纹理和采样器信息通过单个 .texref 句柄访问。在独立模式下,纹理和采样器信息各自具有自己的句柄,允许它们被单独定义并在程序中的使用位置组合。在独立模式下,.texref 类型的描述采样器属性的字段将被忽略,因为这些属性由 .samplerref 变量定义。

表 10 和 表 11 列出了统一和独立纹理模式下每种类型的命名成员。这些成员及其值与纹理 HW 类中定义的方法和值以及通过 API 公开的值具有精确的映射关系。

成员 |

.texref 值 |

.surfref 值 |

|---|---|---|

|

以元素为单位 |

|

|

以元素为单位 |

|

|

以元素为单位 |

|

|

对应于源语言 API 的 |

|

|

对应于源语言 API 的 |

|

|

|

N/A |

|

|

N/A |

|

|

N/A |

|

作为纹理数组中纹理的数量 |

作为表面数组中表面的数量 |

|

作为 mipmapped 纹理中的级别数 |

N/A |

|

作为多采样纹理中的样本数 |

N/A |

|

N/A |

|

5.3.1. 纹理和表面属性

字段 width、height 和 depth 指定纹理或表面的大小,以每个维度中的元素数量为单位。

channel_data_type 和 channel_order 字段使用对应于源语言 API 的枚举类型指定纹理或表面的这些属性。例如,有关 PTX 当前支持的 OpenCL 枚举类型,请参阅通道数据类型和通道顺序字段。

5.3.2. 采样器属性

normalized_coords 字段指示纹理或表面是否使用 [0.0, 1.0) 范围内的归一化坐标,而不是 [0, N) 范围内的非归一化坐标。如果未指定值,则默认值由运行时系统根据源语言设置。

filter_mode 字段指定如何根据输入的纹理坐标计算纹理读取返回的值。

addr_mode_{0,1,2} 字段定义了每个维度中的寻址模式,该模式确定如何处理超出范围的坐标。

有关这些属性的更多详细信息,请参阅CUDA C++ 编程指南。

成员 |

.samplerref 值 |

.texref 值 |

.surfref 值 |

|---|---|---|---|

|

N/A |

以元素为单位 |

|

|

N/A |

以元素为单位 |

|

|

N/A |

以元素为单位 |

|

|

N/A |

对应于源语言 API 的 |

|

|

N/A |

对应于源语言 AP 的 |

|

|

N/A |

|

N/A |

|

|

N/A |

N/A |

|

|

已忽略 |

N/A |

|

|

N/A |

N/A |

|

N/A |

作为纹理数组中纹理的数量 |

作为表面数组中表面的数量 |

|

N/A |

作为 mipmapped 纹理中的级别数 |

N/A |

|

N/A |

作为多采样纹理中的样本数 |

N/A |

|

N/A |

N/A |

|

在独立纹理模式下,采样器属性在独立的 .samplerref 变量中携带,并且这些字段在 .texref 变量中被禁用。在独立纹理模式下,还有一个额外的采样器属性 force_unnormalized_coords 可用。

force_unnormalized_coords 字段是 .samplerref 变量的属性,允许采样器覆盖纹理头 normalized_coords 属性。此字段仅在独立纹理模式下定义。当 True 时,纹理头设置将被覆盖,并使用非归一化坐标;当 False 时,将使用纹理头设置。

force_unnormalized_coords 属性用于编译 OpenCL;在 OpenCL 中,归一化坐标的属性在采样器头中携带。为了将 OpenCL 编译为 PTX,纹理头始终使用设置为 True 的 normalized_coords 初始化,并且基于 OpenCL 采样器的 normalized_coords 标志(取反)映射到 PTX 级别的 force_unnormalized_coords 标志。

使用这些类型的变量可以在模块作用域或内核入口参数列表中声明。在模块作用域中,这些变量必须位于 .global 状态空间中。作为内核参数,这些变量在 .param 状态空间中声明。

例子

.global .texref my_texture_name;

.global .samplerref my_sampler_name;

.global .surfref my_surface_name;

当在模块作用域中声明时,可以使用静态表达式列表初始化这些类型,这些表达式将值赋给命名的成员。

例子

.global .texref tex1;

.global .samplerref tsamp1 = { addr_mode_0 = clamp_to_border,

filter_mode = nearest

};

5.3.3. 通道数据类型和通道顺序字段

channel_data_type 和 channel_order 字段具有与源语言 API 相对应的枚举类型。目前,OpenCL 是唯一定义这些字段的源语言。表 13 和 表 12 显示了 OpenCL 1.0 版本中为通道数据类型和通道顺序定义的枚举值。

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.4. 变量

在 PTX 中,变量声明描述了变量的类型及其状态空间。除了基本类型之外,PTX 还支持简单聚合对象的类型,例如向量和数组。

5.4.1. 变量声明

所有数据存储都通过变量声明来指定。每个变量都必须驻留在上一节中枚举的状态空间之一中。

变量声明命名了变量驻留的空间、其类型和大小、其名称、可选的数组大小、可选的初始化器以及变量的可选固定地址。

谓词变量只能在寄存器状态空间中声明。

示例

.global .u32 loc;

.reg .s32 i;

.const .f32 bias[] = {-1.0, 1.0};

.global .u8 bg[4] = {0, 0, 0, 0};

.reg .v4 .f32 accel;

.reg .pred p, q, r;

5.4.2. 向量

支持有限长度的向量类型。长度为 2 和 4 的任何非谓词基本类型的向量可以通过在类型前加上 .v2 或 .v4 来声明。向量必须基于基本类型,并且可以驻留在寄存器空间中。向量的长度不能超过 128 位;例如,不允许使用 .v4 .f64。三元素向量可以使用 .v4 向量来处理,其中第四个元素提供填充。这对于三维网格、纹理等来说是一种常见情况。

示例

.global .v4 .f32 V; // a length-4 vector of floats

.shared .v2 .u16 uv; // a length-2 vector of unsigned ints

.global .v4 .b8 v; // a length-4 vector of bytes

默认情况下,向量变量与其总大小(向量长度乘以基本类型大小)的倍数对齐,以启用向量加载和存储指令,这些指令需要地址与访问大小的倍数对齐。

5.4.3. 数组声明

提供数组声明是为了允许程序员保留空间。要声明数组,变量名称后跟维度声明,类似于 C 中的固定大小数组声明。每个维度的大小都是常量表达式。

示例

.local .u16 kernel[19][19];

.shared .u8 mailbox[128];

数组的大小指定应保留多少个元素。对于上面数组 *kernel* 的声明,保留了 19*19 = 361 个半字,总共 722 字节。

当使用初始化器声明时,可以省略数组的第一个维度。第一个数组维度的大小由数组初始化器中元素的数量决定。

示例

.global .u32 index[] = { 0, 1, 2, 3, 4, 5, 6, 7 };

.global .s32 offset[][2] = { {-1, 0}, {0, -1}, {1, 0}, {0, 1} };

数组 *index* 有八个元素,数组 *offset* 是一个 4x2 的数组。

5.4.4. 初始化器

声明的变量可以使用类似于 C/C++ 的语法指定初始值,其中变量名称后跟等号和变量的初始值或多个值。标量采用单个值,而向量和数组采用花括号内的嵌套值列表(嵌套与声明的维度匹配)。

与 C 中一样,数组初始化器可能是不完整的,即,初始化器元素的数量可能少于相应数组维度的范围,剩余的数组位置初始化为指定数组类型的默认值。

示例

.const .f32 vals[8] = { 0.33, 0.25, 0.125 };

.global .s32 x[3][2] = { {1,2}, {3} };

等同于

.const .f32 vals[8] = { 0.33, 0.25, 0.125, 0.0, 0.0, 0.0, 0.0, 0.0 };

.global .s32 x[3][2] = { {1,2}, {3,0}, {0,0} };

目前,变量初始化仅支持常量和全局状态空间。常量和全局状态空间中没有显式初始化器的变量默认初始化为零。外部变量声明中不允许使用初始化器。

出现在初始化器中的变量名称表示变量的地址;这可以用于静态初始化指向变量的指针。初始化器还可以包含 *var+offset* 表达式,其中 *offset* 是添加到 *var* 地址的字节偏移量。只有 .global 或 .const 状态空间中的变量才能在初始化器中使用。默认情况下,结果地址是变量状态空间中的偏移量(就像使用 mov 指令获取变量地址的情况一样)。提供了一个运算符 generic(),用于为初始化器中使用的变量创建通用地址。

从 PTX ISA 版本 7.1 开始,提供了一个运算符 mask(),其中 mask 是一个整数立即数。mask() 运算符中唯一允许的表达式是整数常量表达式和表示变量地址的符号表达式。mask() 运算符从初始化器中使用的表达式中提取 n 个连续位,并将这些位插入到初始化变量的最低位置。要提取的位数 n 和起始位置由整数立即数 mask 指定。PTX ISA 版本 7.1 仅支持从变量地址提取从字节边界开始的单个字节。PTX ISA 版本 7.3 支持将整数常量表达式作为 mask() 运算符中的操作数。

支持的 mask 值包括:0xFF、0xFF00、0XFF0000、0xFF000000、0xFF00000000、0xFF0000000000、0xFF000000000000、0xFF00000000000000。

示例

.const .u32 foo = 42;

.global .u32 bar[] = { 2, 3, 5 };

.global .u32 p1 = foo; // offset of foo in .const space

.global .u32 p2 = generic(foo); // generic address of foo

// array of generic-address pointers to elements of bar

.global .u32 parr[] = { generic(bar), generic(bar)+4,

generic(bar)+8 };

// examples using mask() operator are pruned for brevity

.global .u8 addr[] = {0xff(foo), 0xff00(foo), 0xff0000(foo), ...};

.global .u8 addr2[] = {0xff(foo+4), 0xff00(foo+4), 0xff0000(foo+4),...}

.global .u8 addr3[] = {0xff(generic(foo)), 0xff00(generic(foo)),...}

.global .u8 addr4[] = {0xff(generic(foo)+4), 0xff00(generic(foo)+4),...}

// mask() operator with integer const expression

.global .u8 addr5[] = { 0xFF(1000 + 546), 0xFF00(131187), ...};

注意

PTX 3.1 重新定义了初始化器中全局变量的默认寻址方式,从通用地址到全局状态空间中的偏移量。旧版 PTX 代码被视为对初始化器中使用的每个全局变量都具有隐式 generic() 运算符。PTX 3.1 代码应在初始化器中包含显式 generic() 运算符,使用 cvta.global 在运行时形成通用地址,或使用 ld.global 从非通用地址加载。

出现在初始化器中的设备函数名称表示函数中第一条指令的地址;这可以用于初始化函数指针表,以便与间接调用一起使用。从 PTX ISA 版本 3.1 开始,内核函数名称可以用作初始化器,例如,初始化内核函数指针表,以便与 CUDA 动态并行性一起使用以从 GPU 启动内核。有关详细信息,请参阅 *CUDA 动态并行性编程指南*。

标签不能在初始化器中使用。

保存变量或函数地址的变量应为 .u8 或 .u32 或 .u64 类型。

仅当使用 mask() 运算符时,才允许使用类型 .u8。

除 .f16、.f16x2 和 .pred 外的所有类型都允许使用初始化器。

示例

.global .s32 n = 10;

.global .f32 blur_kernel[][3]

= {{.05,.1,.05},{.1,.4,.1},{.05,.1,.05}};

.global .u32 foo[] = { 2, 3, 5, 7, 9, 11 };

.global .u64 ptr = generic(foo); // generic address of foo[0]

.global .u64 ptr = generic(foo)+8; // generic address of foo[2]

5.4.5. 对齐

可以变量声明中指定所有可寻址变量的存储字节对齐方式。对齐方式使用可选的 .align*字节计数* 说明符在状态空间说明符之后立即指定。变量将对齐到字节计数的整数倍的地址。对齐值字节计数必须是 2 的幂。对于数组,对齐指定整个数组的起始地址的地址对齐,而不是单个元素的地址对齐。

标量和数组变量的默认对齐方式是基本类型大小的倍数。向量变量的默认对齐方式是整个向量大小的倍数。

示例

// allocate array at 4-byte aligned address. Elements are bytes.

.const .align 4 .b8 bar[8] = {0,0,0,0,2,0,0,0};

请注意,所有访问内存的 PTX 指令都要求地址与访问大小的倍数对齐。内存指令的访问大小是在内存中访问的总字节数。例如,ld.v4.b32 的访问大小为 16 字节,而 atom.f16x2 的访问大小为 4 字节。

5.4.6. 参数化变量名

由于 PTX 支持虚拟寄存器,因此编译器前端生成大量寄存器名称非常常见。PTX 支持一种语法,用于创建一组具有公共前缀字符串并附加整数后缀的变量,而不是要求显式声明每个名称。

例如,假设程序使用大量(例如一百个).b32 变量,命名为 %r0、%r1、…、%r99。这些 100 个寄存器变量可以声明如下

.reg .b32 %r<100>; // declare %r0, %r1, ..., %r99

此简写语法可以与任何基本类型和任何状态空间一起使用,并且可以在前面加上对齐说明符。数组变量不能以这种方式声明,也不允许使用初始化器。

5.4.7. 变量属性

可以使用可选的 .attribute 指令声明变量,该指令允许指定变量的特殊属性。关键字 .attribute 后跟括号内的属性规范。多个属性用逗号分隔。

变量和函数属性指令:.attribute 描述了 .attribute 指令。

5.4.8. 变量和函数属性指令:.attribute

.attribute

变量和函数属性

描述

用于指定变量或函数的特殊属性。

支持以下属性。

.managed-

.managed属性指定变量将分配在统一虚拟内存环境中的位置,在该环境中,主机和系统中的其他设备可以直接引用该变量。此属性只能用于 .global 状态空间中的变量。有关详细信息,请参阅 *CUDA UVM-Lite 编程指南*。 .unified-

.unified属性指定函数在主机和系统中的其他设备上具有相同的内存地址。整数常量uuid1和uuid2分别指定与函数或变量关联的唯一标识符的高 64 位和低 64 位。此属性只能用于设备函数或.global状态空间中的变量。具有.unified属性的变量是只读的,必须通过在ld指令的地址操作数上指定.unified限定符来加载,否则行为未定义。

PTX ISA 注释

在 PTX ISA 版本 4.0 中引入。

对函数属性的支持在 PTX ISA 版本 8.0 中引入。

目标 ISA 注释

.managed属性需要sm_30或更高版本。.unified属性需要sm_90或更高版本。

示例

.global .attribute(.managed) .s32 g;

.global .attribute(.managed) .u64 x;

.global .attribute(.unified(19,95)) .f32 f;

.func .attribute(.unified(0xAB, 0xCD)) bar() { ... }

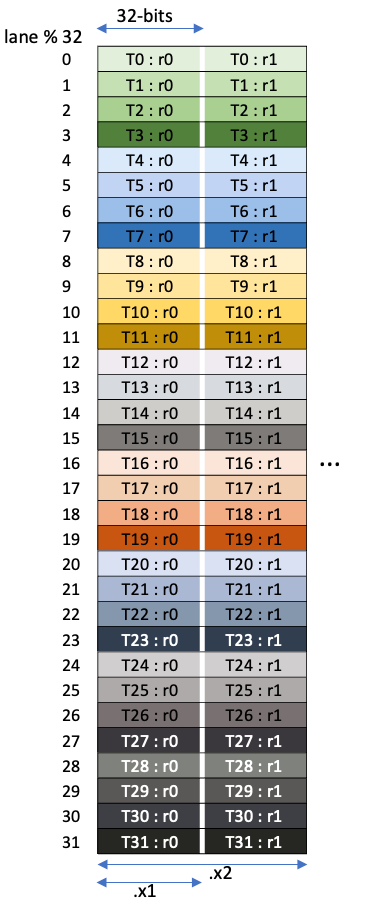

5.5. 张量

张量是内存中的多维矩阵结构。张量由以下属性定义

维度

每个维度上的维度大小

单个元素类型

每个维度上的张量步幅

PTX 支持可以对张量数据进行操作的指令。PTX 张量指令包括

在全球内存和共享内存之间复制数据

使用源数据缩减目标张量数据。

张量数据可以通过各种 wmma.mma、mma 和 wgmma.mma_async 指令进行操作。

PTX 张量指令将全局内存中的张量数据视为多维结构,并将共享内存中的数据视为线性数据。

5.5.1. 张量维度、大小和格式

张量可以具有以下维度:1D、2D、3D、4D 或 5D。

每个维度都有一个大小,表示沿该维度的元素数量。元素可以具有以下类型之一

位大小类型:

.b32、.b64子字节类型:

.b4x16、.b4x16_p64、.b6x16_p32、.b6p2x16整数:

.u8、.u16、.u32、.s32、.u64、.s64浮点和备用浮点:

.f16、.bf16、.tf32、.f32、.f64(四舍五入到最接近的偶数)。

张量可以在每个维度的末尾具有填充,以便为后续维度中的数据提供对齐。张量步幅可用于指定每个维度中的填充量。

5.5.1.1. 子字节类型

5.5.1.1.1. 子字节类型的填充和对齐

子字节类型预计在全局内存中连续打包,张量复制指令将通过附加空白空间来扩展它们,如下所示

类型

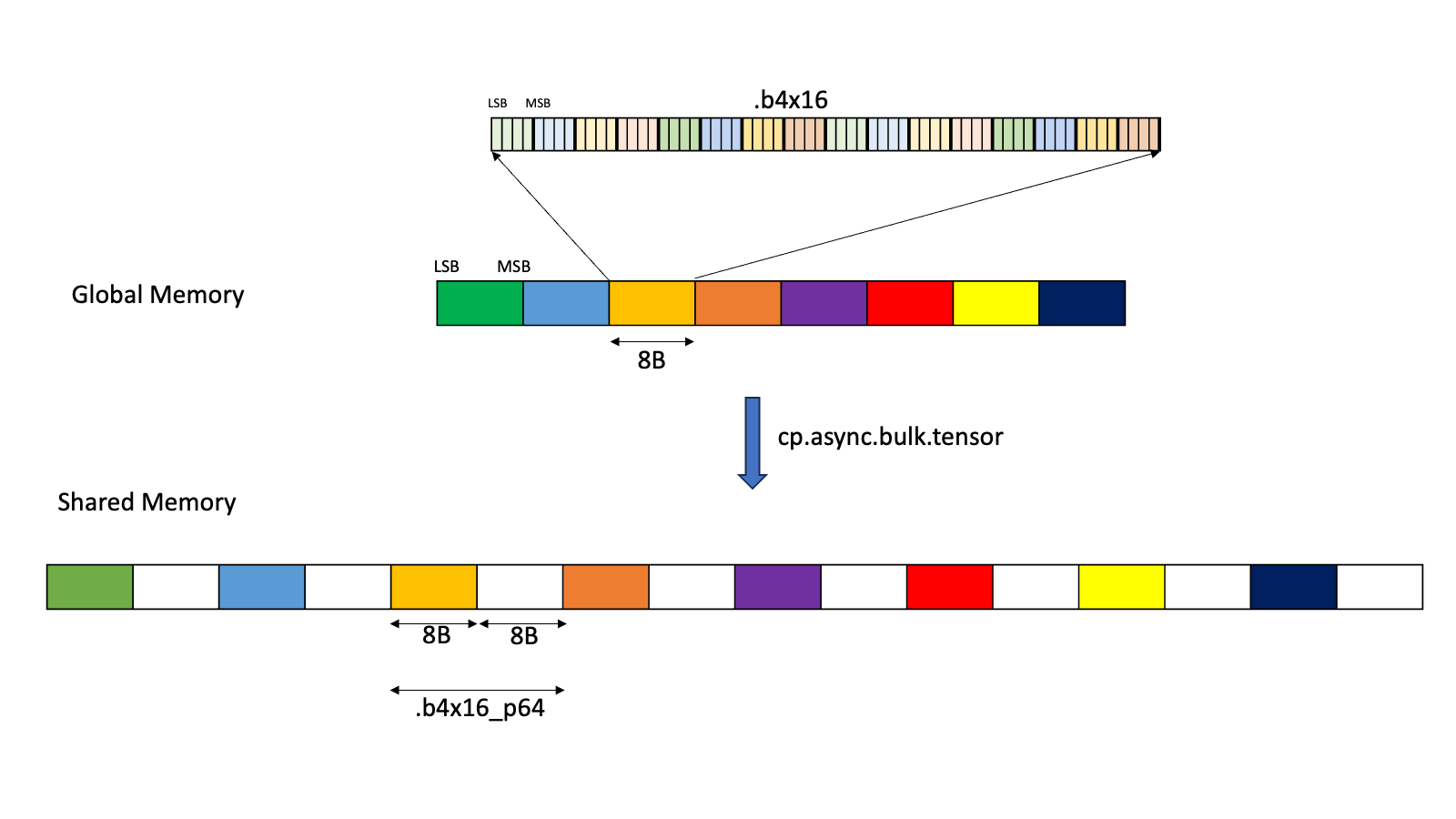

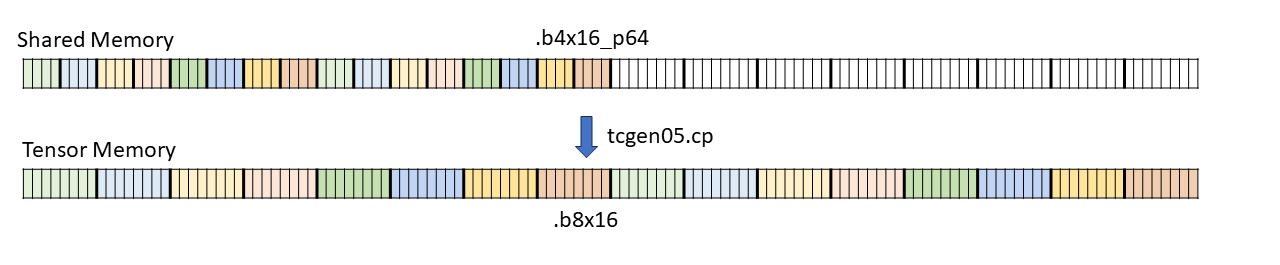

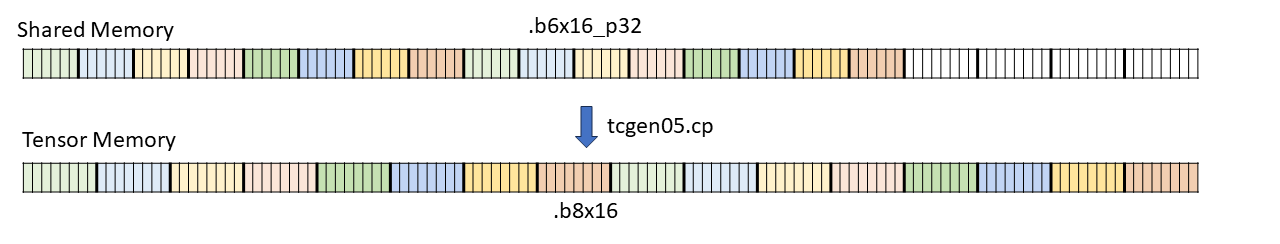

.b4x16:使用此类型,不涉及填充,并且 64 位容器中打包的十六个.b4元素在共享内存和全局内存之间按原样复制。-

类型

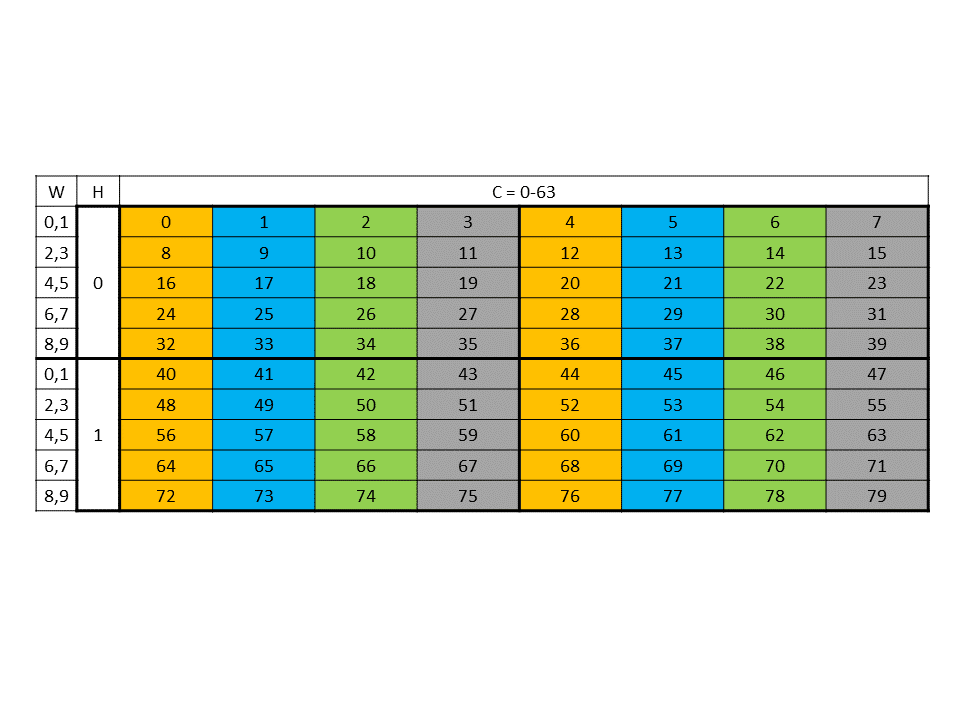

.b4x16_p64:使用此类型,从全局内存复制十六个连续的 4 位数据到共享内存,并附加 64 位填充,如 图 5 所示

图 5 .b4x16_p64 的布局

添加的填充区域未初始化。

-

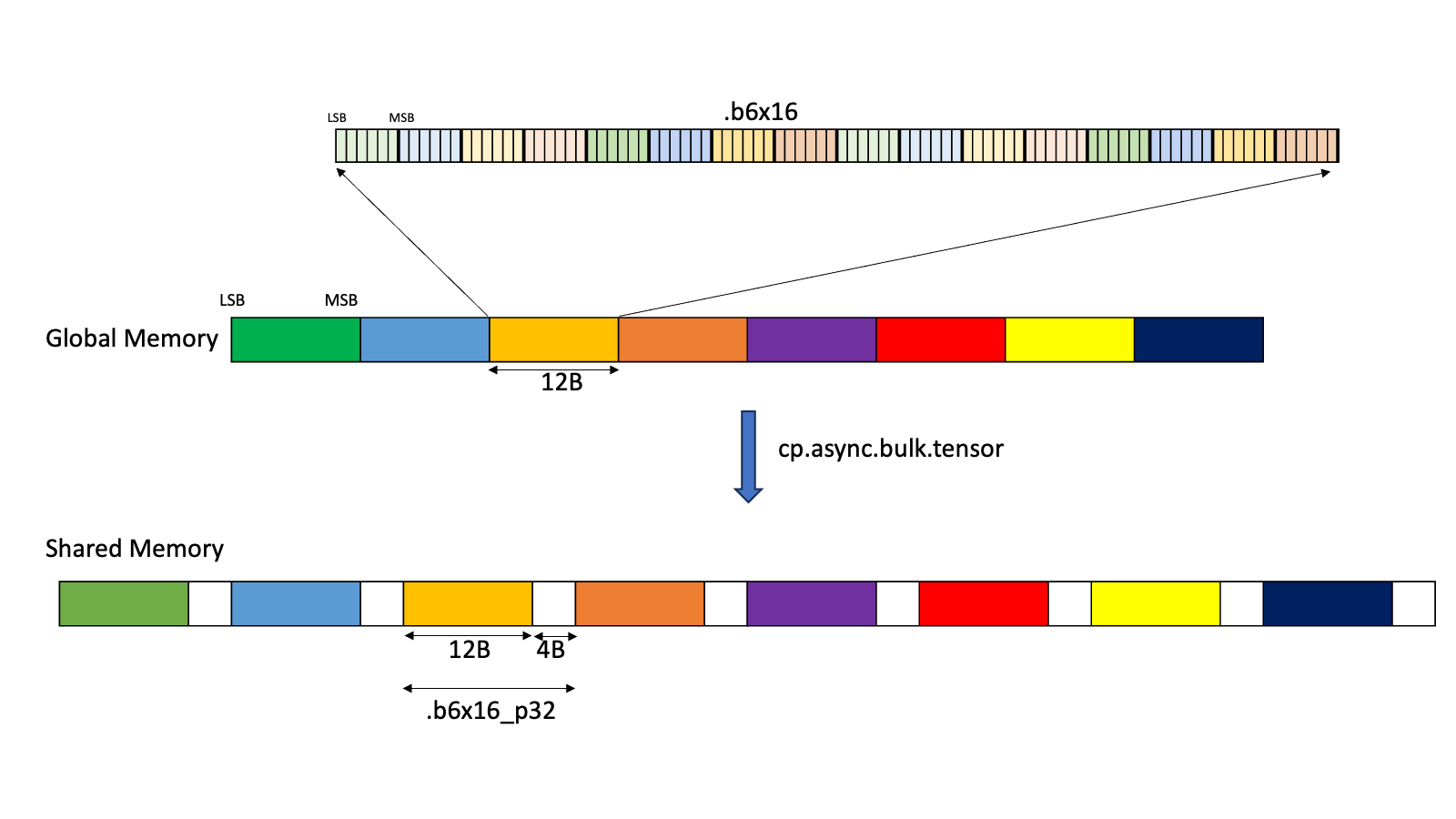

类型

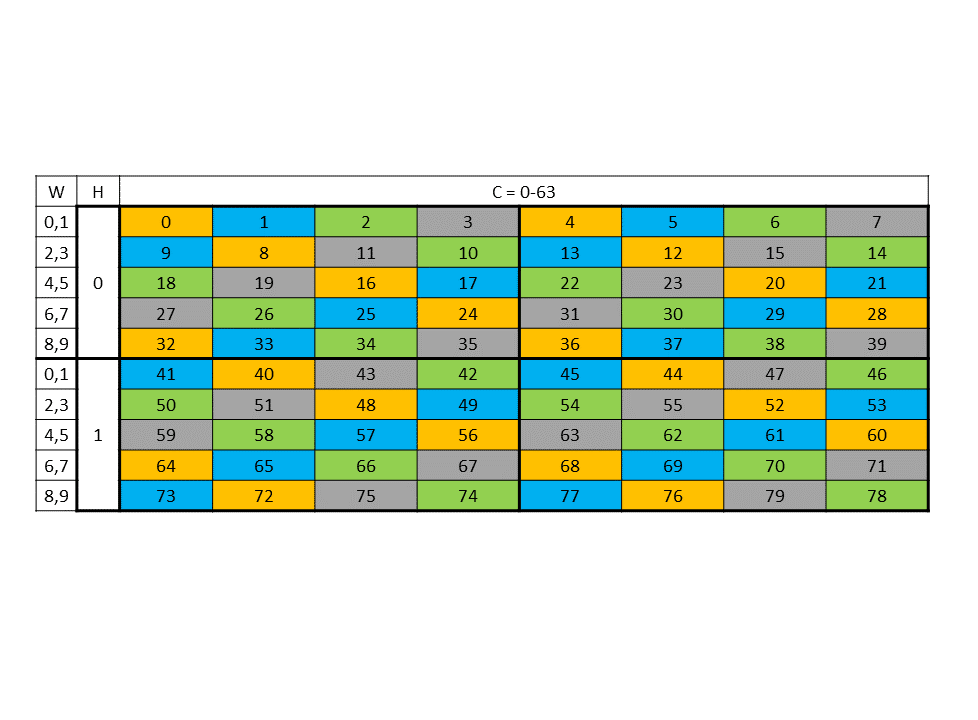

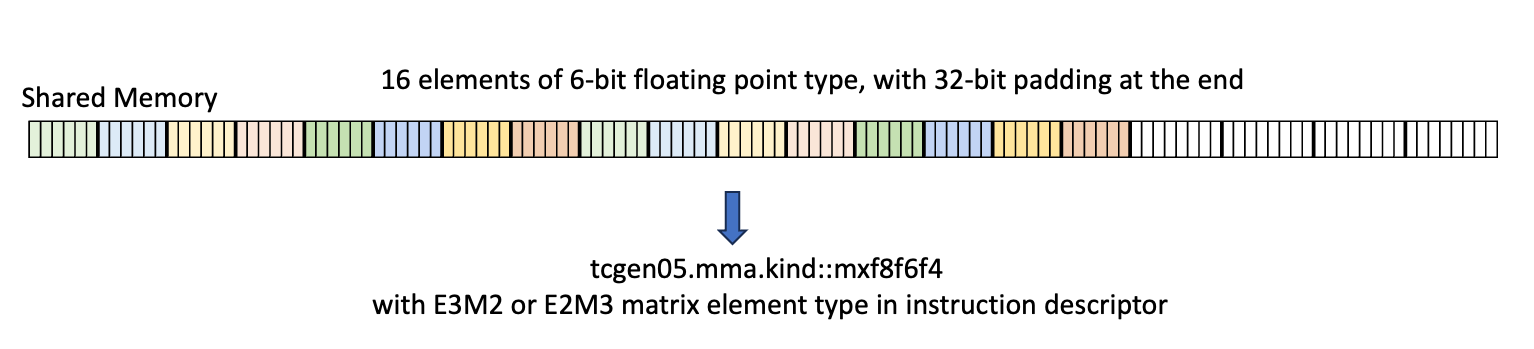

.b6x16_p32:使用此类型,从全局内存复制十六个 6 位数据到共享内存,并附加 32 位填充,如 图 6 所示

图 6 .b6x16_p32 的布局

添加的填充区域未初始化。

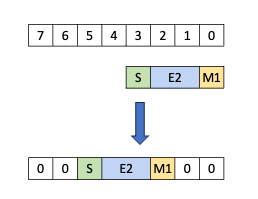

-

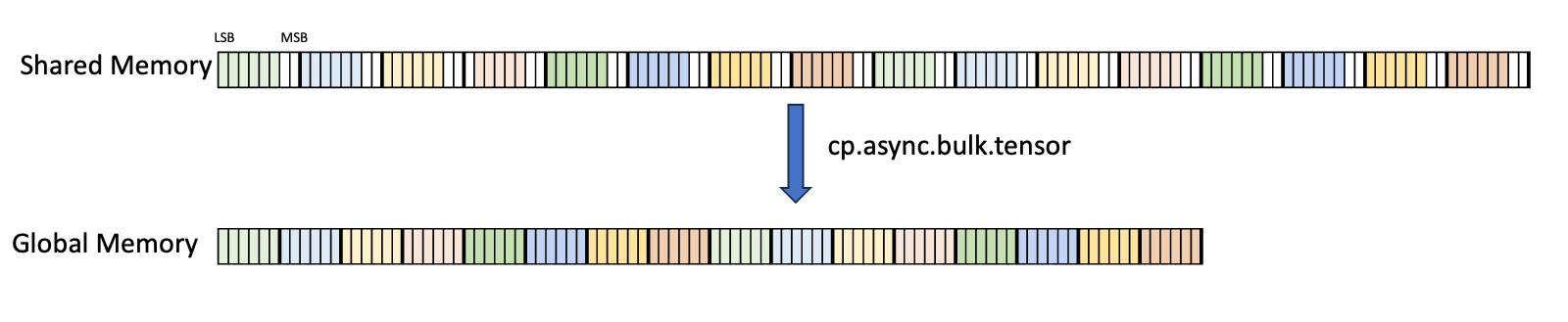

类型

.b6p2x16:使用此类型,从共享内存复制十六个元素(每个元素在 LSB 处包含 6 位数据,在 MSB 处包含 2 位填充)到全局内存,方法是丢弃 2 位填充数据并将 6 位数据连续打包,如 图 7 所示

图 7 .b6p2x16 的布局

对于 .b6x16_p32 和 .b4x16_p64,添加的填充区域未初始化。

类型 .b6x16_p32 和 .b6p2x16 在描述符中共享相同的编码值(值 15),因为这两种类型适用于不同类型的张量复制操作

类型 |

有效的张量复制方向 |

|---|---|

|

|

|

|

5.5.2. 张量访问模式

张量数据可以通过两种模式访问

-

平铺模式

在平铺模式下,源多维张量布局在目标位置保留。

-

Im2col 模式

在 im2col 模式下,源张量的边界框中的元素被重新排列到目标位置的列中。有关更多详细信息,请参阅 此处。

5.5.3. 平铺模式

本节讨论张量和平铺模式下的张量访问如何工作。

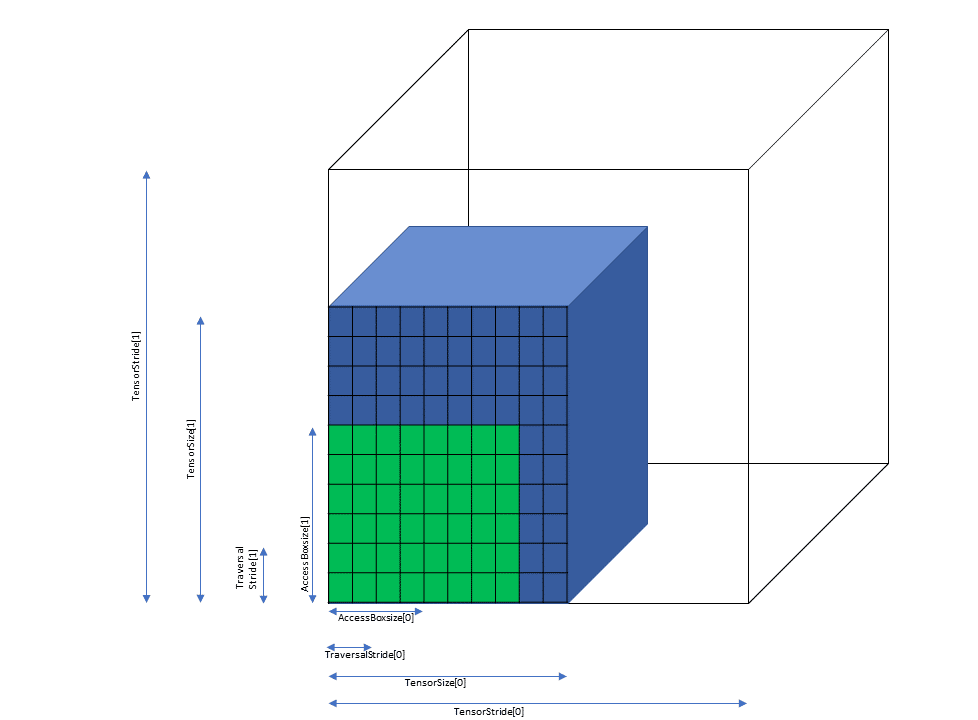

5.5.3.1. 边界框

张量可以以称为 *边界框* 的块访问。边界框具有与它们访问的张量相同的维度。每个边界框的大小必须是 16 字节的倍数。边界框的地址也必须与 16 字节对齐。

边界框具有以下访问属性

边界框维度大小

超出边界访问模式

遍历步幅

PTX 张量指令中指定的张量坐标指定边界框的起始偏移量。边界框的起始偏移量以及其余边界框信息一起用于确定要访问的元素。

5.5.3.2. 遍历步幅

当边界框跨维度迭代张量时,遍历步幅指定要跳过的确切元素数。如果不需要跳过,则必须指定默认值 1。

维度 0 中的遍历步幅可用于 交错布局。对于非交错布局,维度 0 中的遍历步幅必须始终为 1。

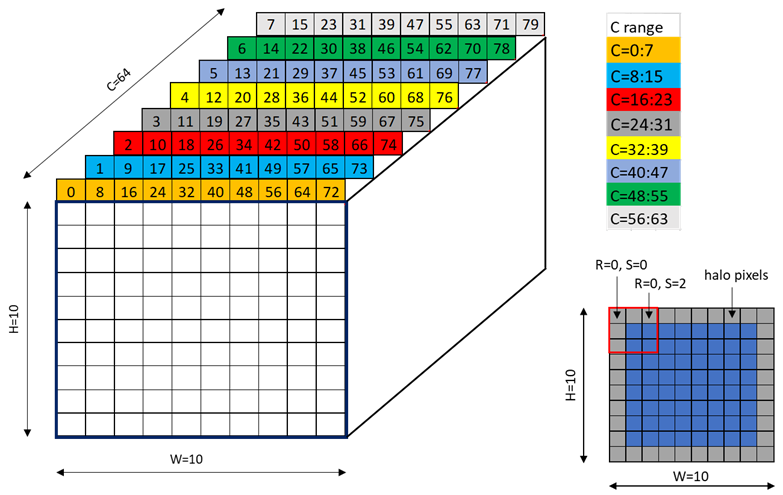

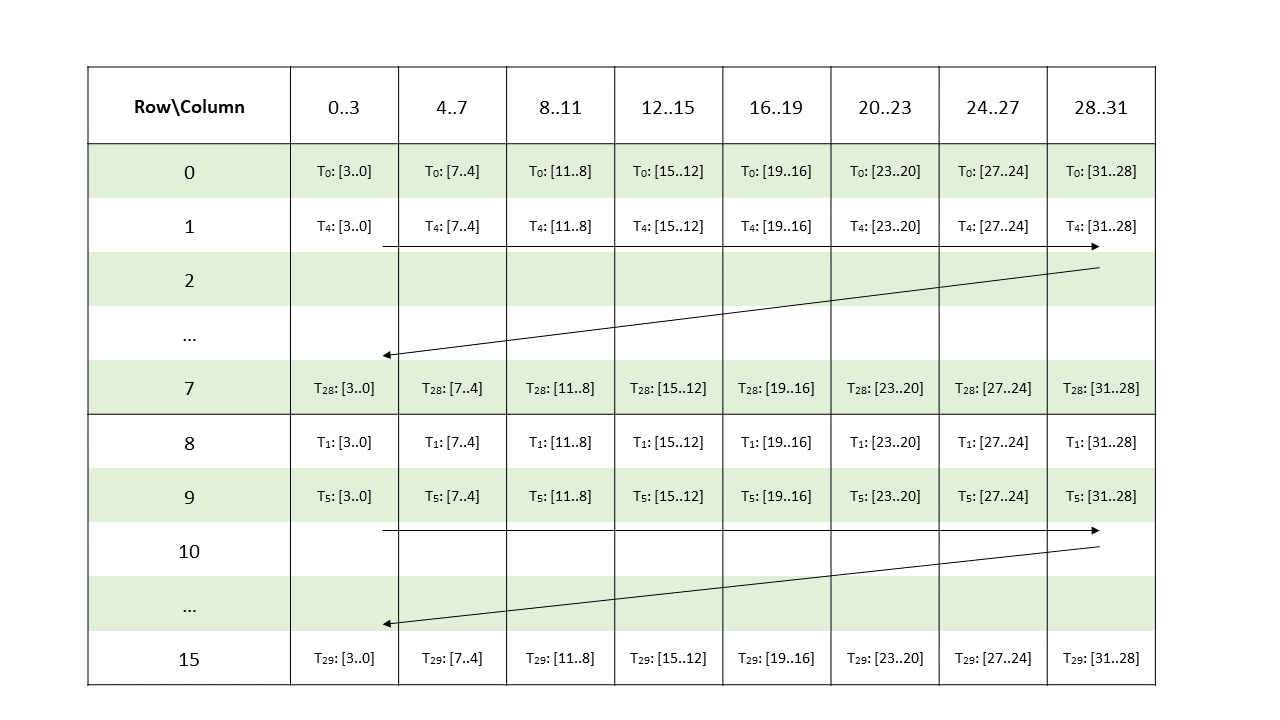

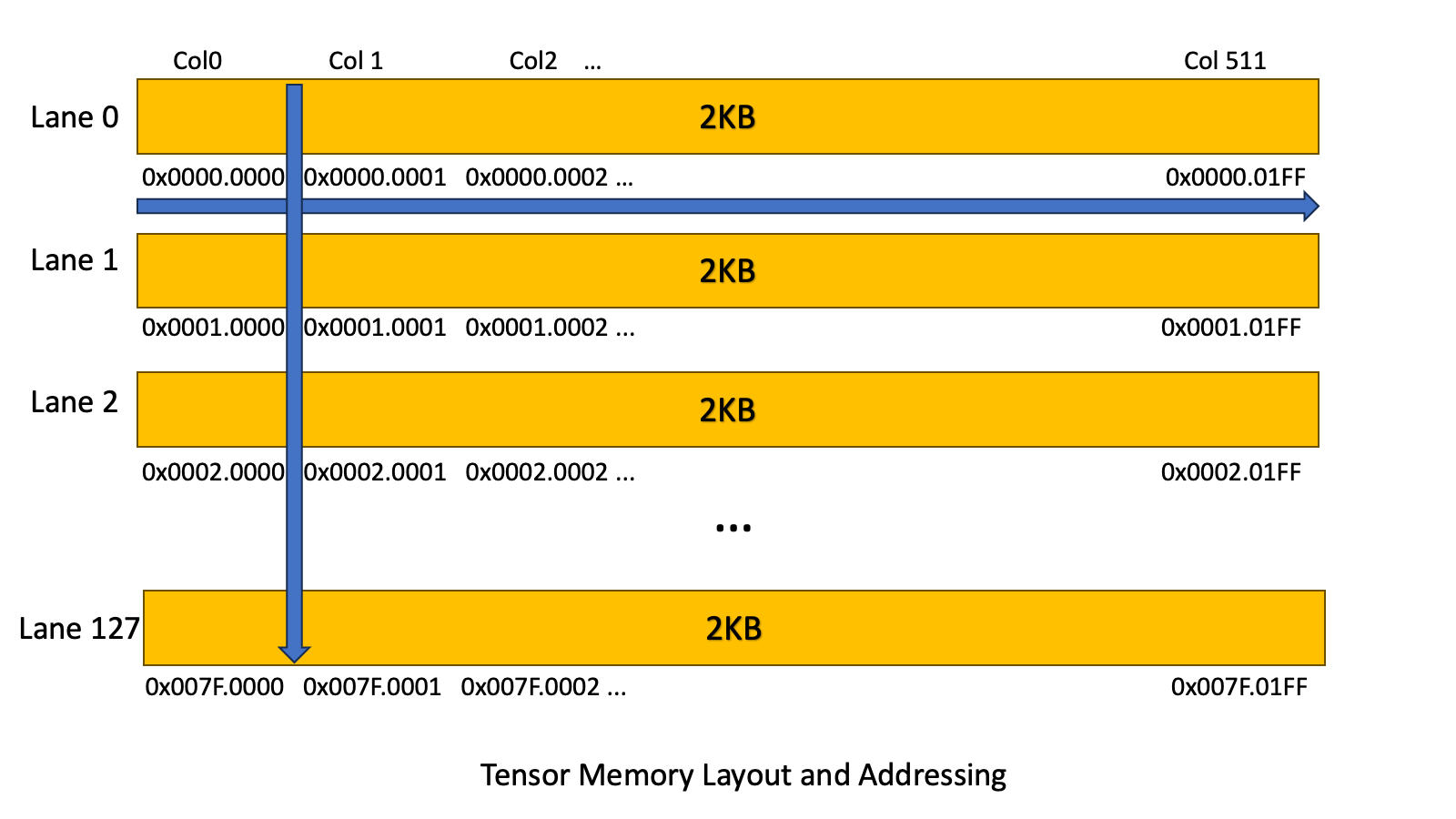

图 8 说明了张量、张量大小、张量步幅、边界框大小和遍历步幅。

图 8 平铺模式边界框、张量大小和遍历步幅

5.5.3.3. 超出边界访问

当边界框在任何维度上跨越张量边界时,PTX 张量操作可以检测并处理这种情况。有两种模式

-

零填充模式

边界框中落在张量边界之外的元素设置为 0。

-

OOB-NaN填充模式边界框中落在张量边界之外的元素设置为特殊的 NaN,称为

OOB-NaN。

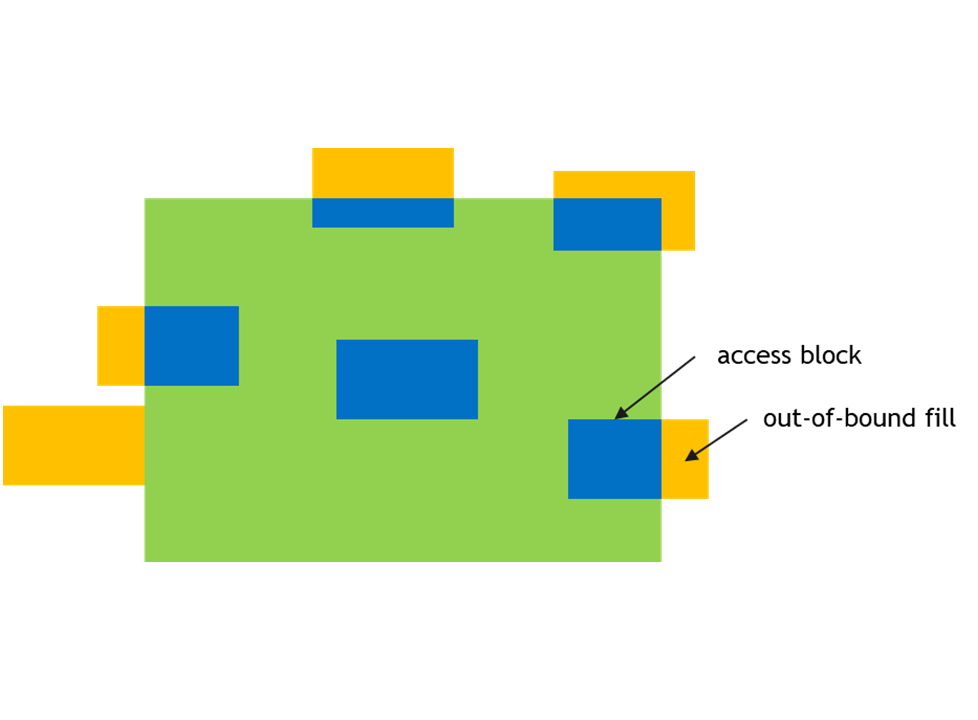

图 9 显示了超出边界访问的示例。

图 9 超出边界访问

5.5.3.4. Tile::scatter4 和 Tile::gather4 模式

这些模式类似于平铺模式,但限制是这些模式仅适用于 2D 张量数据。Tile::scatter4 和 Tile::gather4 模式用于访问张量数据的多个不连续行。

在 Tile::scatter4 模式下,单个 2D 源张量被分成 2D 目标张量中的四行。在 Tile::gather4 模式下,源 2D 张量中的四行被组合以形成单个 2D 目标张量。

这些模式适用于四行,因此指令将采用

维度 0 上的四个张量坐标

维度 1 上的一个张量坐标

对于 .tile::scatter4 和 .tile::gather4 模式,不支持交错布局。

平铺模式的所有其他约束和规则也适用于这些模式。

5.5.3.4.1. 边界框

对于 Tile::scatter4 和 Tile::gather4 模式,四个请求坐标将在张量空间中形成四个边界框。

图 10 显示了以起始坐标 (1, 2)、(1, 5)、(1, 0) 和 (1, 9) 为例的情况。

维度 0 中边界框的大小表示行的长度。维度 1 中边界框的大小必须为 1。

图 10 tiled::scatter4/tiled::gather4 模式边界框示例

5.5.4. Im2col 模式

Im2col 模式支持以下张量维度:3D、4D 和 5D。在此模式下,张量数据被视为一批图像,具有以下属性

N:批次中的图像数量

D、H、W:3D 图像的大小(深度、高度和宽度)

C:每个图像元素的通道数

以上属性与 3D、4D 和 5D 张量关联,如下所示

维度 |

N/D/H/W/C 适用性 |

|---|---|

3D |

NWC |

4D |

NHWC |

5D |

NDHWC |

5.5.4.1. 边界框

在 im2col 模式下,边界框在 DHW 空间中定义。沿其他维度的边界由每列像素数和每像素通道数参数指定,如下所述。

边界框的维度比张量维度小两个。

以下属性描述了如何在 im2col 模式下访问元素

边界框左下角

边界框右上角

每列像素数

每像素通道数

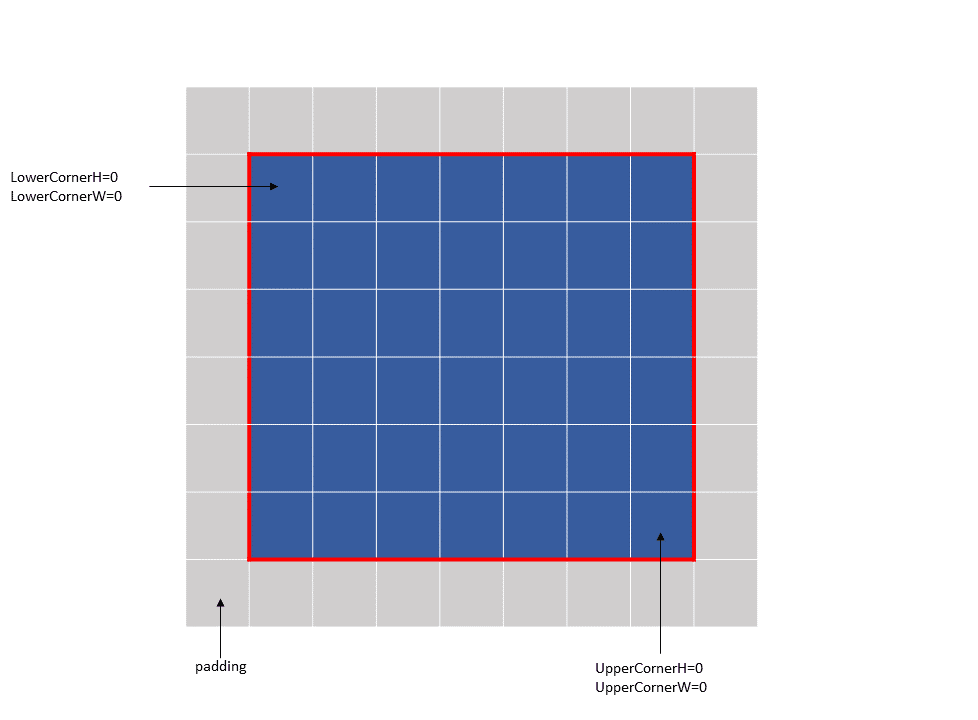

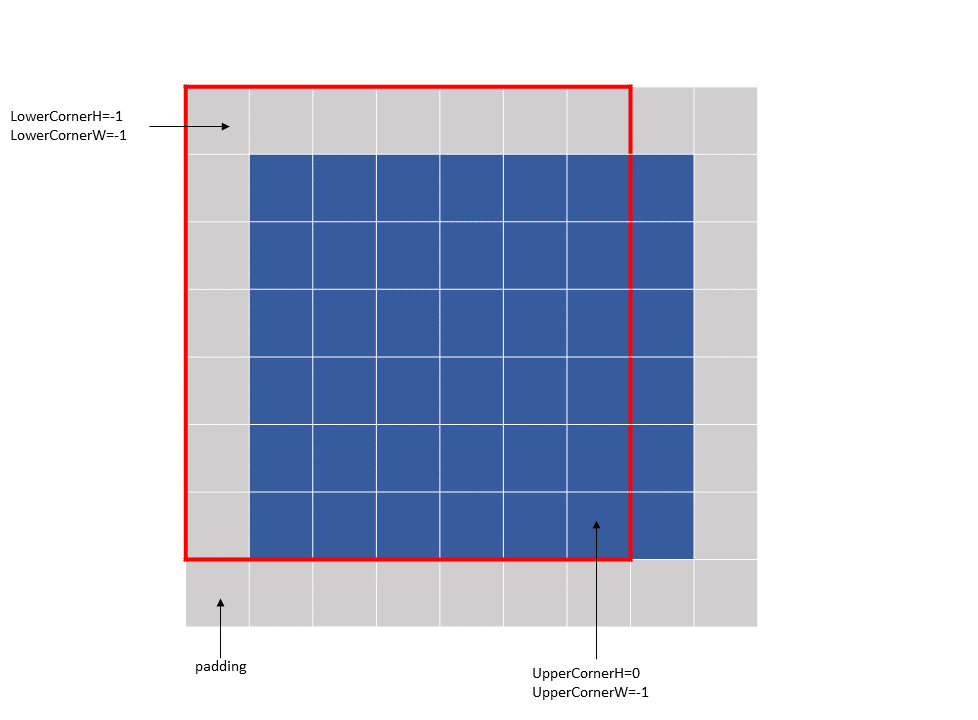

Bounding-box Lower-Corner 和 Bounding-box Upper-Corner 指定了 DHW 空间中边界框的两个对角。Bounding-box Lower-Corner 指定了坐标最小的角,而 Bounding-box Upper-Corner 指定了坐标最大的角。

Bounding-box Upper- 和 Lower-Corners 是 16 位有符号值,其限制因维度而异,如下所示

3D |

4D |

5D |

|

|---|---|---|---|

Upper- / Lower- Corner 尺寸 |

[-215, 215-1] |

[-27, 27-1] |

[-24, 24-1] |

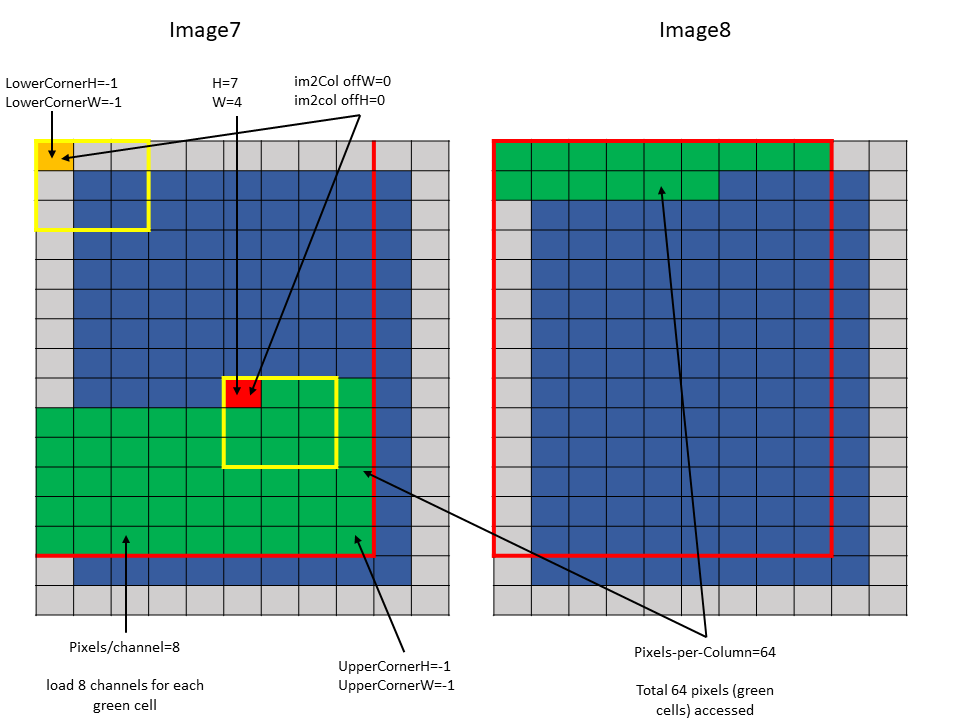

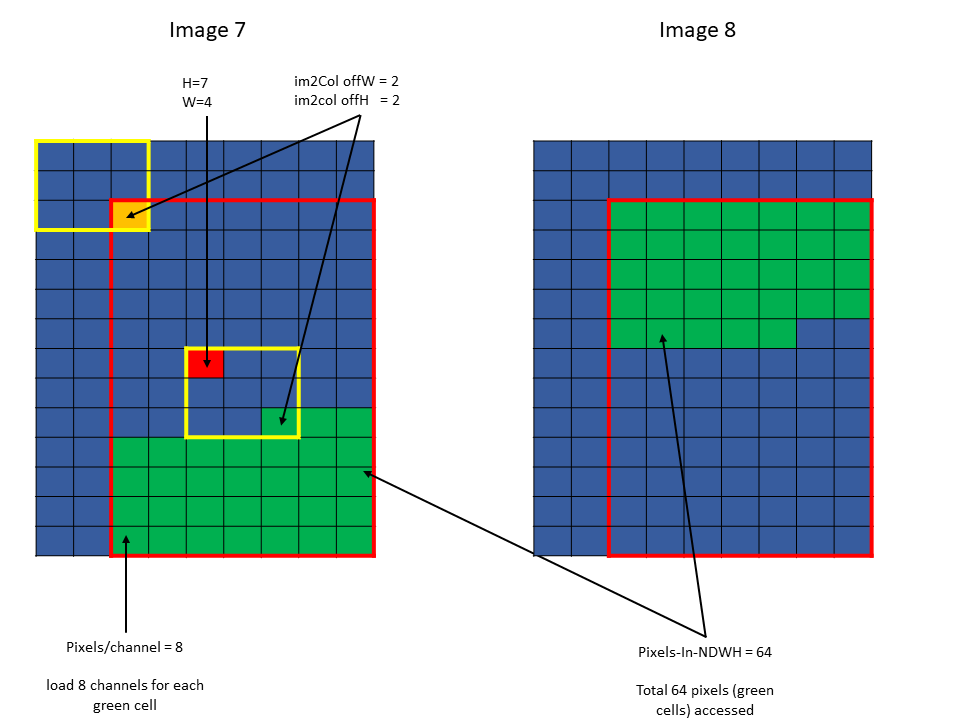

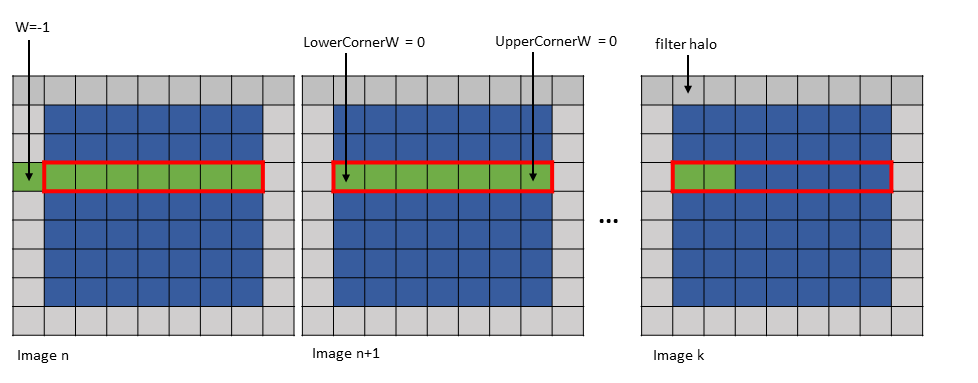

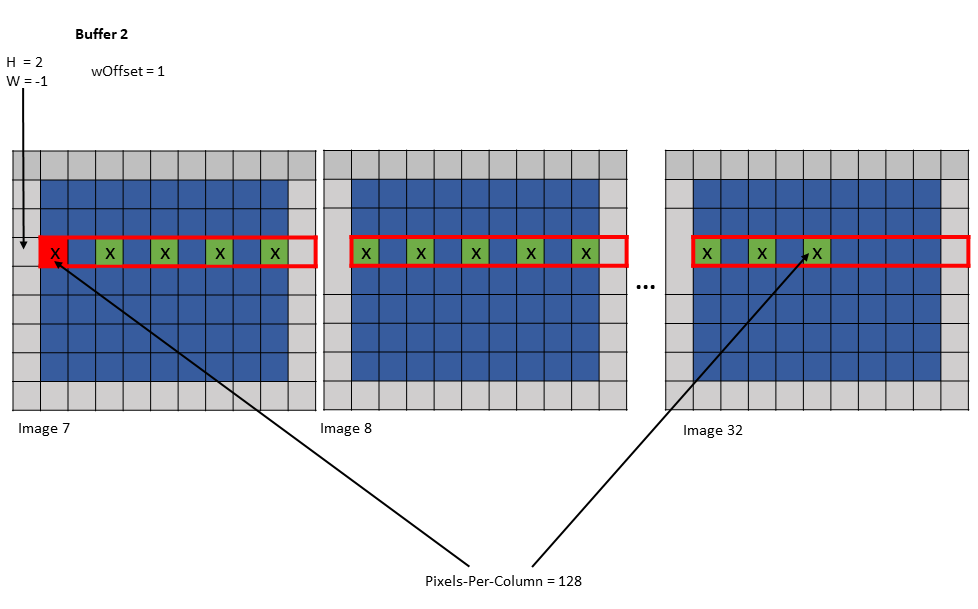

图 11 和 图 12 显示了 Upper-Corners 和 Lower-Corners。

图 11 im2col 模式边界框示例 1

图 12 im2col 模式边界框示例 2

Bounding-box Upper- 和 Lower- Corners 仅指定边界,而不指定要访问的元素数量。Pixels-per-Column 指定了 NDHW 空间中要访问的元素数量。

Channels-per-Pixel 指定了跨 C 维度要访问的元素数量。

张量坐标在 PTX 张量指令中指定,在不同维度上的行为有所不同

跨 N 和 C 维度:指定沿维度的起始偏移量,类似于平铺模式。

跨 DHW 维度:指定卷积滤波器基在张量空间中的位置。滤波器角位置必须在边界框内。

在 im2col 模式下,PTX 张量指令中指定的 im2col 偏移量被添加到滤波器基坐标,以确定张量空间中元素访问的起始位置。

im2col 偏移量的大小因维度而异,其有效范围如下所示

3D |

4D |

5D |

|

|---|---|---|---|

im2col 偏移量范围 |

[0, 216-1] |

[0, 28-1] |

[0, 25-1] |

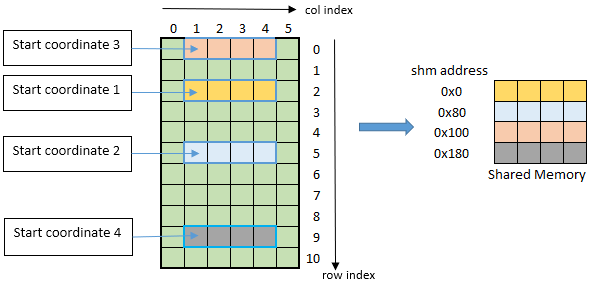

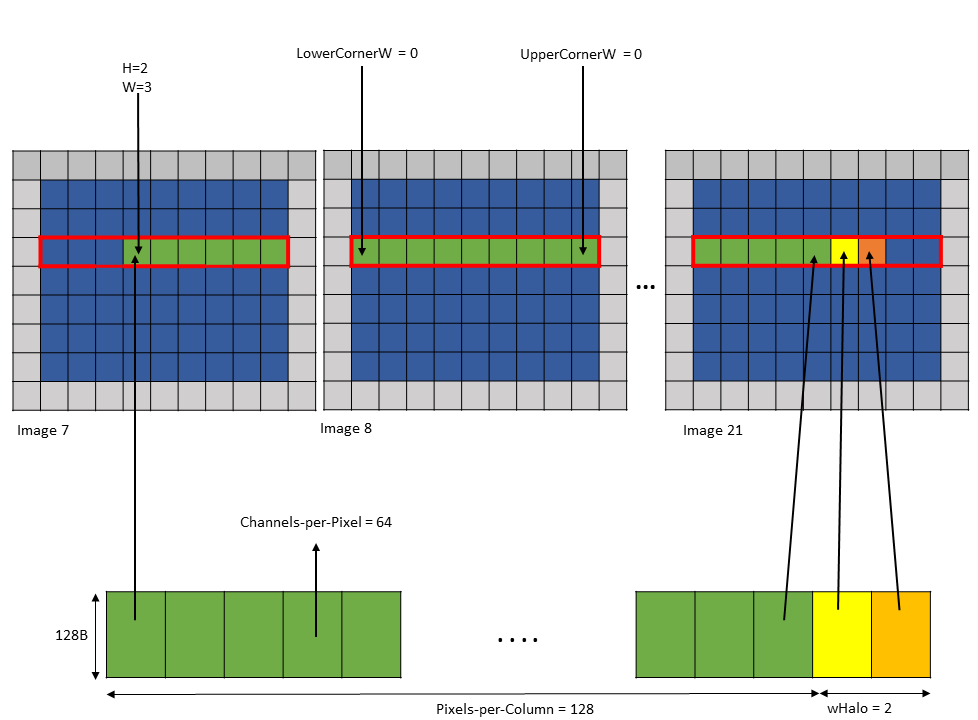

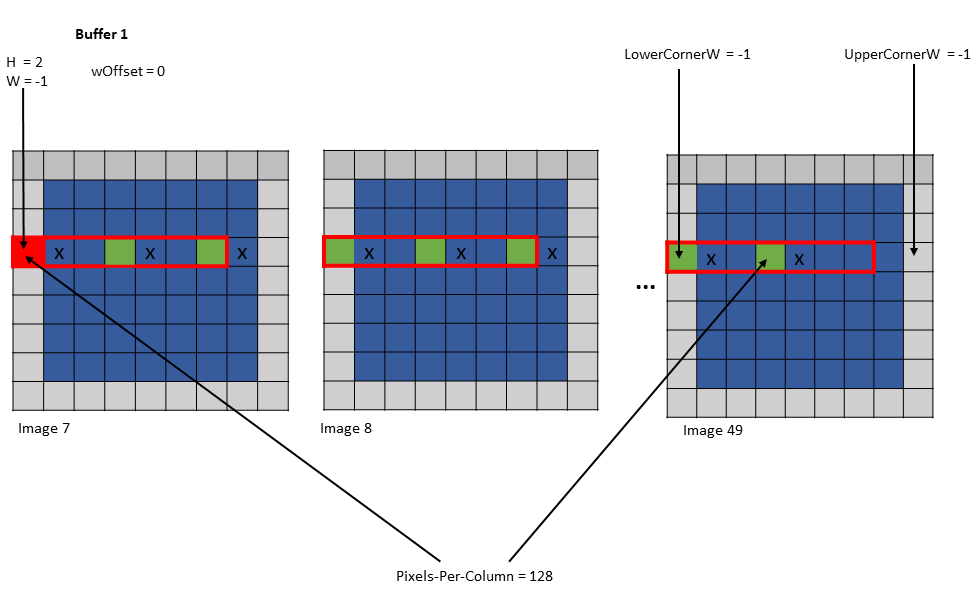

以下是一些 im2col 模式访问的示例

-

示例 1 (图 13)

Tensor Size[0] = 64 Tensor Size[1] = 9 Tensor Size[2] = 14 Tensor Size[3] = 64 Pixels-per-Column = 64 channels-per-pixel = 8 Bounding-Box Lower-Corner W = -1 Bounding-Box Lower-Corner H = -1 Bounding-Box Upper-Corner W = -1 Bounding-Box Upper-Corner H = -1. tensor coordinates = (7, 7, 4, 0) im2col offsets : (0, 0)

图 13 im2col 模式示例 1

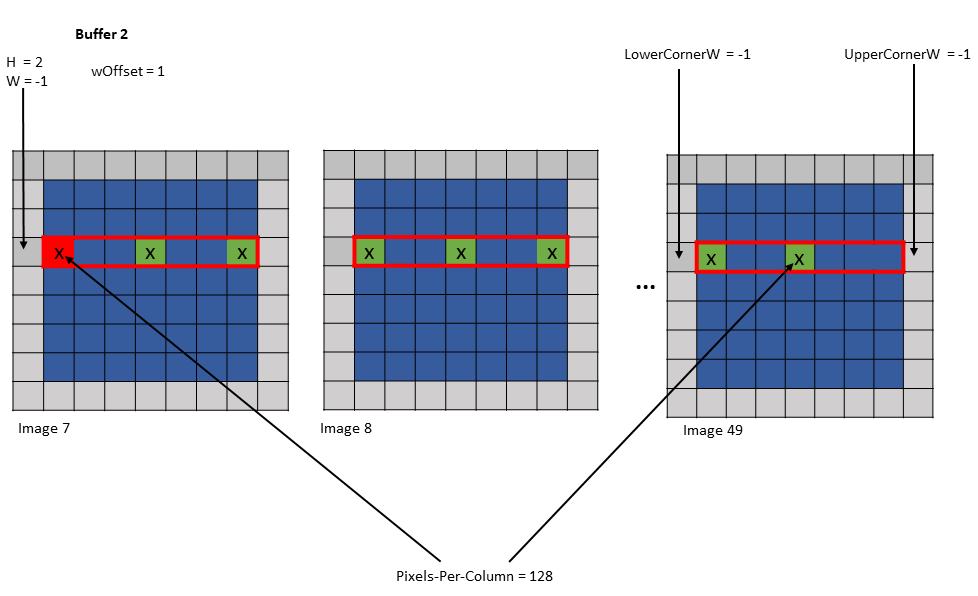

-

示例 2 (图 14)

Tensor Size[0] = 64 Tensor Size[1] = 9 Tensor Size[2] = 14 Tensor Size[3] = 64 Pixels-per-Column = 64 channels-per-pixel = 8 Bounding-Box Lower-Corner W = 0 Bounding-Box Lower-Corner H = 0 Bounding-Box Upper-Corner W = -2 Bounding-Box Upper-Corner H = -2 tensor coordinates = (7, 7, 4, 0) im2col offsets: (2, 2)

图 14 im2col 模式示例 2

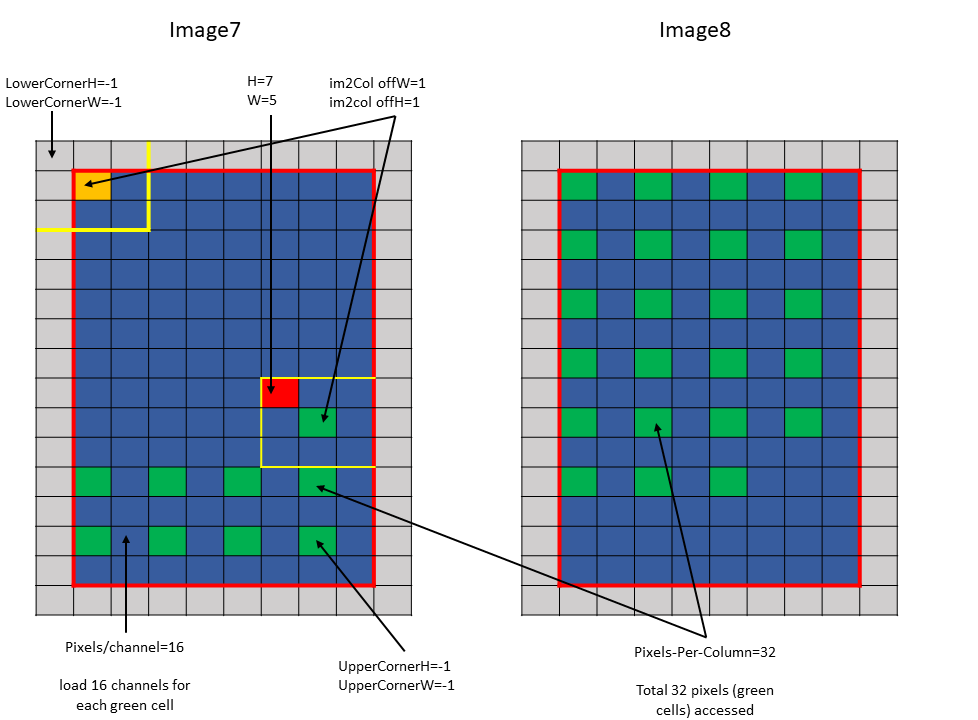

5.5.4.2. 遍历步幅

在 im2col 模式下,遍历步幅不像平铺模式那样影响访问的元素(或像素)总数。在 im2col 模式下,Pixels-per-Column 决定了访问的元素总数。

沿 D、H 和 W 维度遍历的元素数量由该维度的遍历步幅进行跨步。

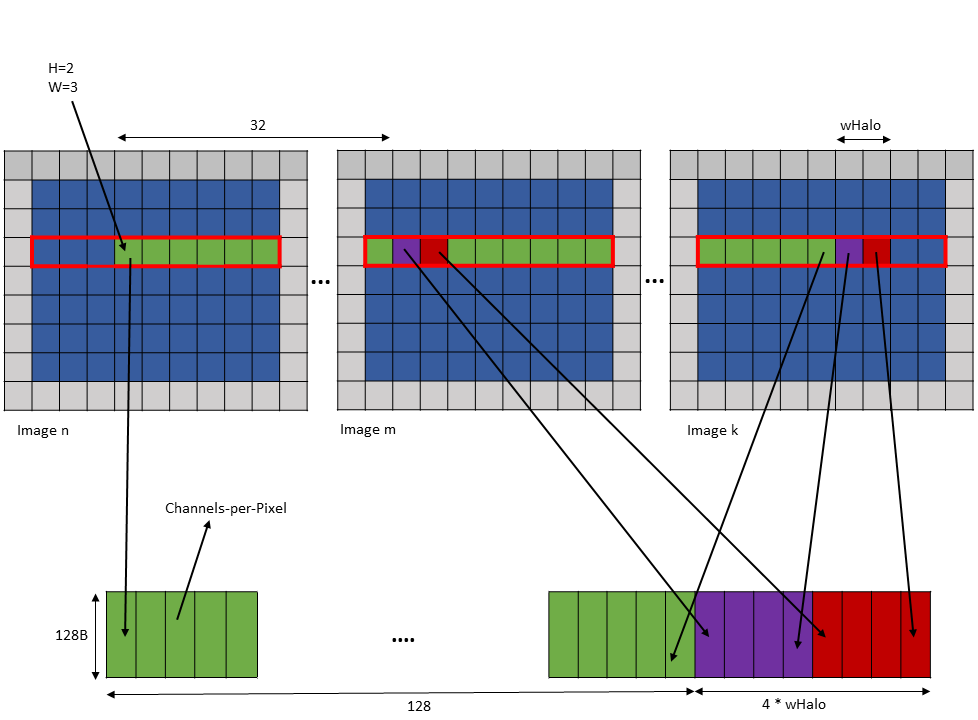

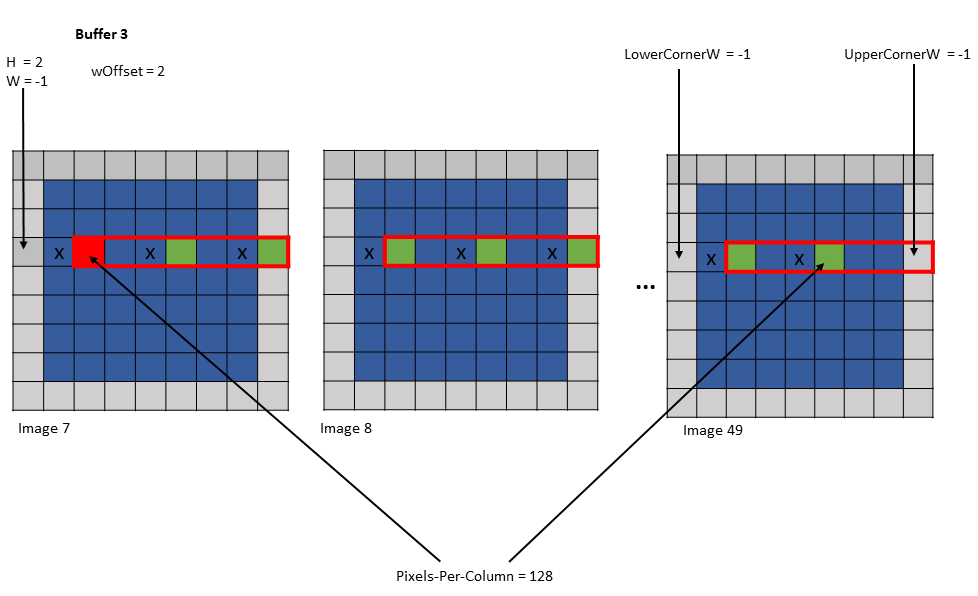

以下示例使用 图 15 说明了使用遍历步幅的访问

Tensor Size[0] = 64

Tensor Size[1] = 8

Tensor Size[2] = 14

Tensor Size[3] = 64

Traversal Stride = 2

Pixels-per-Column = 32

channels-per-pixel = 16

Bounding-Box Lower-Corner W = -1

Bounding-Box Lower-Corner H = -1

Bounding-Box Upper-Corner W = -1

Bounding-Box Upper-Corner H = -1.

Tensor coordinates in the instruction = (7, 7, 5, 0)

Im2col offsets in the instruction : (1, 1)

图 15 im2col 模式遍历步幅示例

5.5.4.3. 越界访问

在 im2col 模式下,当 Pixels-per-Column 指定的 NDHW 空间中请求的像素数量超过图像批次中可用的像素数量时,将执行越界访问。

与平铺模式类似,可以根据指定的填充模式执行零填充或 OOB-NaN 填充。

5.5.5. Im2col::w 和 Im2col::w::128 模式

这些模式与 im2col 模式类似,但限制是元素仅在 W 维度上访问,同时保持 H 和 D 维度恒定。

im2col 模式的所有约束和规则也适用于这些模式。

在 im2col::w::128 模式下访问的元素数量是固定的,等于 128。在 im2col::w 模式下访问的元素数量取决于 TensorMap 中的 Pixels-per-Column 字段。

5.5.5.1. 边界框

在这些模式下,D 和 H 维度中边界框的大小为 1。

PTX 指令中张量坐标参数中的 D 和 H 维度指定了边界框在张量空间中的位置。

边界框 Lower-Corner-W 和边界框 Upper-Corner-W 指定了 W 维度中边界框的两个对角。

PTX 指令中张量坐标参数中的 W 维度指定了要在边界框中访问的第一个元素的位置。

在 im2col::w 模式下加载的像素数量由 TensorMap 中的 Pixels-per-Column 指定。在 im2col::w::128 模式下加载的像素数量始终为 128。因此,在 im2col::w::128 模式下,Pixels-per-Column 被忽略。

图 16 显示了 im2col::w 和 im2col::w:128 模式的示例。

图 16 im2col::w 和 im2col::w::128 模式示例

第一个元素可以位于边界框之外,仅在 W 维度上,并且仅在边界框的左侧。图 17 显示了此示例。

图 17 im2col::w 和 im2col::w::128 模式第一个元素位于边界框外示例

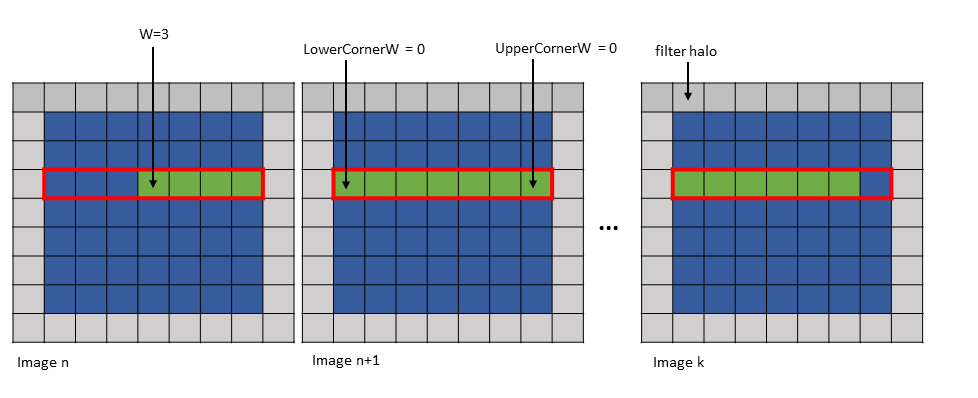

5.5.5.2. 遍历步幅

这类似于 im2col 模式,但例外是仅沿 W 维度遍历的元素数量由 TensorMap 中指定的遍历步幅进行跨步。

5.5.5.3. wHalo

在 im2col::w 模式下,PTX 指令中的 wHalo 参数指定了在图像末尾必须加载多少滤波器光环元素。

在 im2col::w::128 模式下,在沿 W 维度的边界框中每 32 个元素后加载光环元素。PTX 指令中的 wHalo 参数指定了每 32 个元素后必须加载多少光环元素。

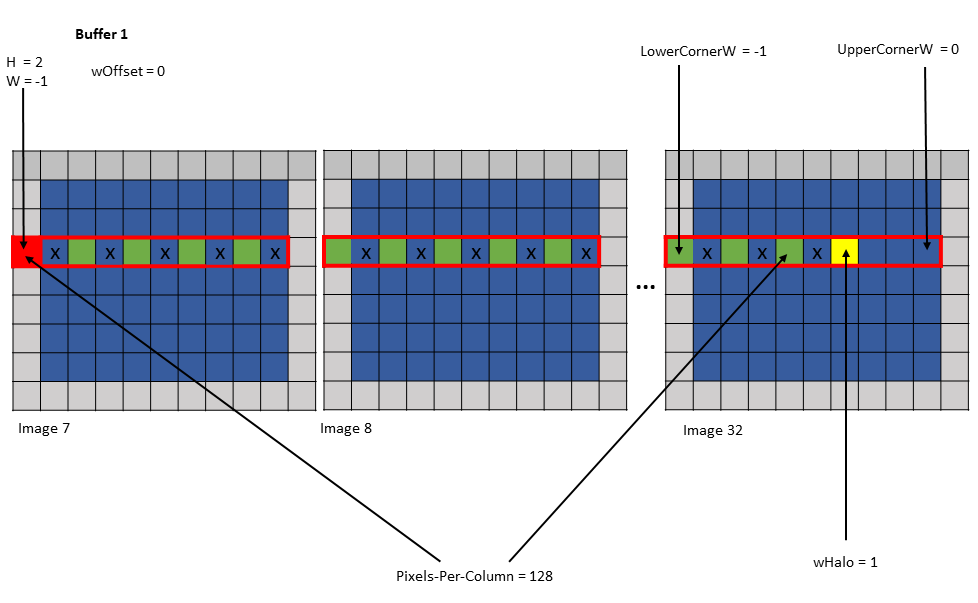

以下是 .im2col::w 模式访问的示例

Tensor Size [0] = 128

Tensor Size [1] = 9

Tensor Size [2] = 7

Tensor Size [3] = 64

Pixels-per-column = 128

Channels-per-pixel = 64

Bounding Box Lower Corner W = 0

Bounding Box Upper Corner W = 0

Tensor Coordinates in the instruction = (7, 2, 3, 0)

wHalo in the instruction = 2 (as 3x3 convolution filter is used)

使用上述参数的张量复制操作加载 128 个像素和两个光环像素,如 图 18 所示。

图 18 使用 im2col::w 模式示例的张量复制操作

光环像素始终加载在共享内存中,紧邻主行像素,如 图 18 所示。

以下是 .im2col::w::128 模式访问的示例

Tensor Size [0] = 128

Tensor Size [1] = 9

Tensor Size [2] = 7

Tensor Size [3] = 64

Channels-per-pixel = 64

Bounding Box Lower Corner W = 0

Bounding Box Upper Corner W = 0

Tensor Coordinates in the instruction = (7, 2, 3, 0)

wHalo in the instruction = 2 (as 3x3 convolution filter is used)

使用上述参数的张量复制操作加载 128 个元素,使得每 32 个元素后,加载 wHalo 数量的元素,如 图 19 所示。

图 19 使用 im2col::w::128 模式示例的张量复制操作

5.5.5.4. wOffset

在卷积计算中,沿 W 维度的相同元素被重用于卷积滤波器足迹内的不同位置。根据像素被使用的次数,像素可以加载到不同的共享内存缓冲区中。每个缓冲区可以由单独的张量复制操作加载。

张量复制和预取指令中的 wOffset 参数调整每个缓冲区的源像素位置。缓冲区的确切位置沿 W 维度使用以下公式进行调整

Bounding Box Lower Corner W += wOffset

Bounding Box Upper Corner W += wOffset

W += wOffset

以下是使用各种 wHalo 和 wOffset 值的张量复制到多个缓冲区的示例

示例 1

Tensor Size [0] = 128

Tensor Size [1] = 9

Tensor Size [2] = 67

Tensor Size [3] = 64

Pixels-per-Column = 128

Channels-per-pixel = 64

Bounding Box Lower Corner W = -1

Bounding Box Upper Corner W = 0

Traversal Stride = 2

Tensor Coordinates in the instruction = (7, 2, -1, 0)

Shared memory buffer 1:

wHalo = 1

wOffset = 0

Shared memory buffer 2:

wHalo = 0

wOffset = 1

图 20 示例 1 的缓冲区 1 的张量复制操作

图 21 示例 1 的缓冲区 2 的张量复制操作

示例 2

Tensor Size [0] = 128

Tensor Size [1] = 7

Tensor Size [2] = 7

Tensor Size [3] = 64

Pixels-per-Column = 128

Channels-per-pixel = 64

Bounding Box Lower Corner W = -1

Bounding Box Upper Corner W = -1

Traversal Stride = 3

Tensor Coordinates in the instruction = (7, 2, -1, 0)

Shared memory buffer 1:

wHalo = 0

wOffset = 0

Shared memory buffer 2:

wHalo = 0

wOffset = 1

Shared memory buffer 3:

wHalo = 0

wOffset = 2

图 22 示例 2 的缓冲区 1 的张量复制操作

图 23 示例 2 的缓冲区 2 的张量复制操作

图 24 示例 2 的缓冲区 3 的张量复制操作

5.5.6. 交错布局

张量可以是交错的,并支持以下交错布局

无交错 (NDHWC)

8 字节交错 (NC/8DHWC8) : C8 在内存中利用 16 字节,假设每个通道 2B。

16 字节交错 (NC/16HWC16) : C16 在内存中利用 32 字节,假设每个通道 4B。

C 信息以切片形式组织,其中连续的 C 元素以 16 字节或 32 字节数量分组。

如果通道总数不是每个切片通道数的倍数,则最后一个切片必须用零填充,使其成为完整的 16B 或 32B 切片。

交错布局仅支持以下维度:3D、4D 和 5D。

交错布局不支持 .im2col::w 和 .im2col::w::128 模式。

5.5.7. 混合模式

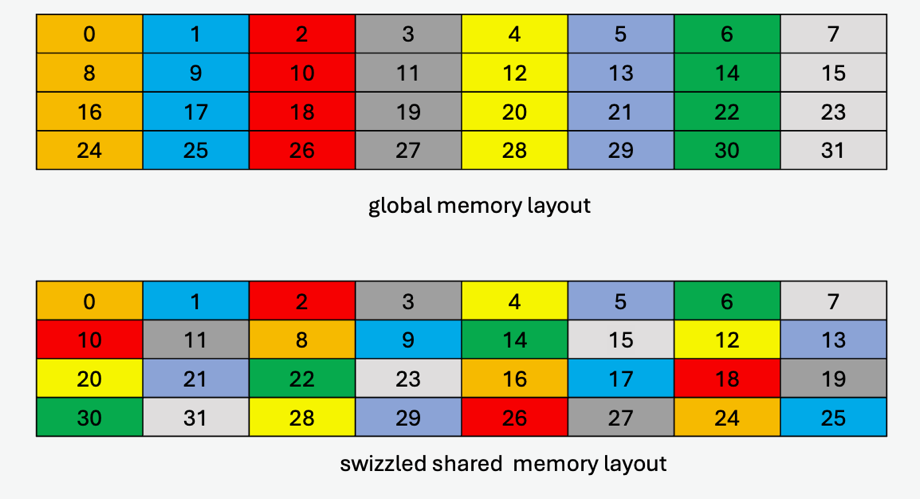

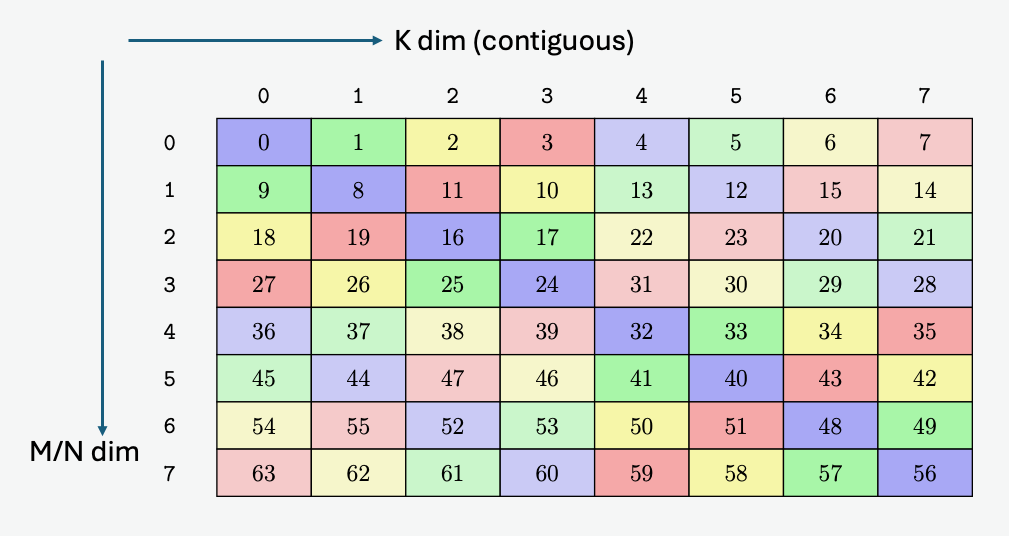

出于访问性能的原因,共享内存中的数据布局可能与全局内存中的数据布局不同。以下描述了各种混合模式

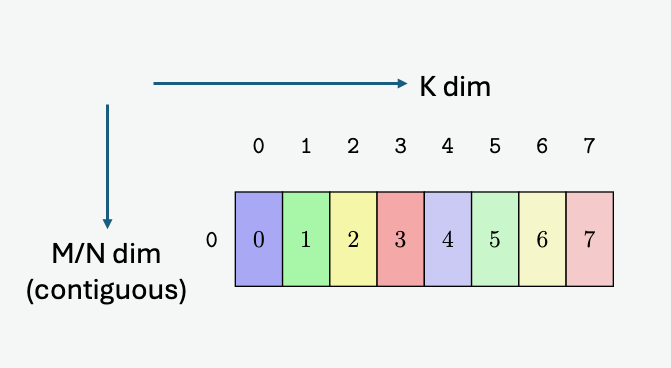

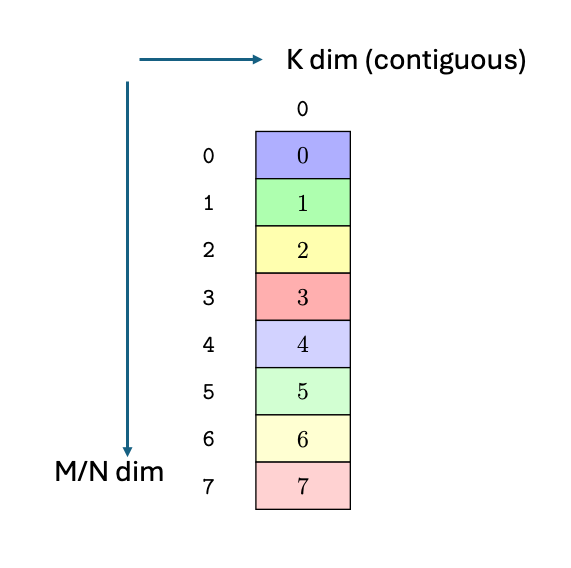

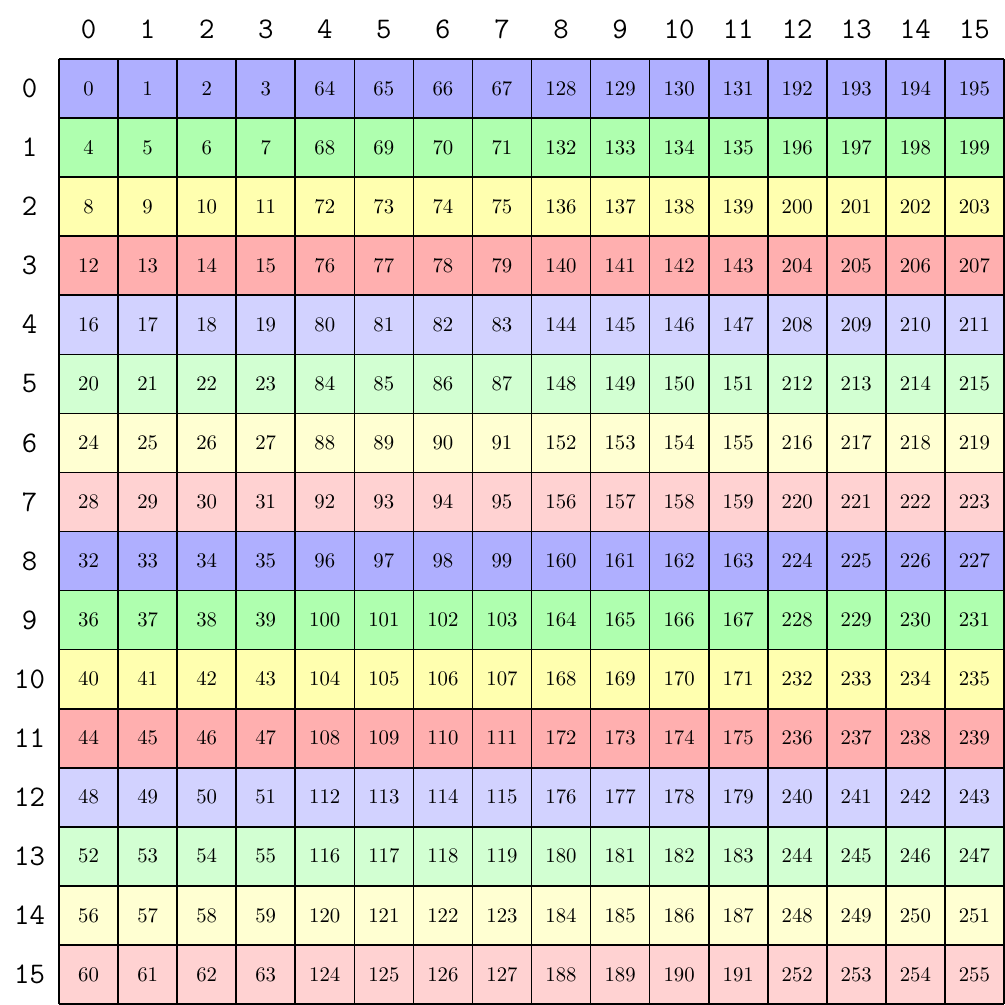

-

无混合模式

在此模式下没有混合,目标数据布局与源数据布局完全相似。

0

1

2

3

4

5

6

7

0

1

2

3

4

5

6

7

… 模式重复 …

-

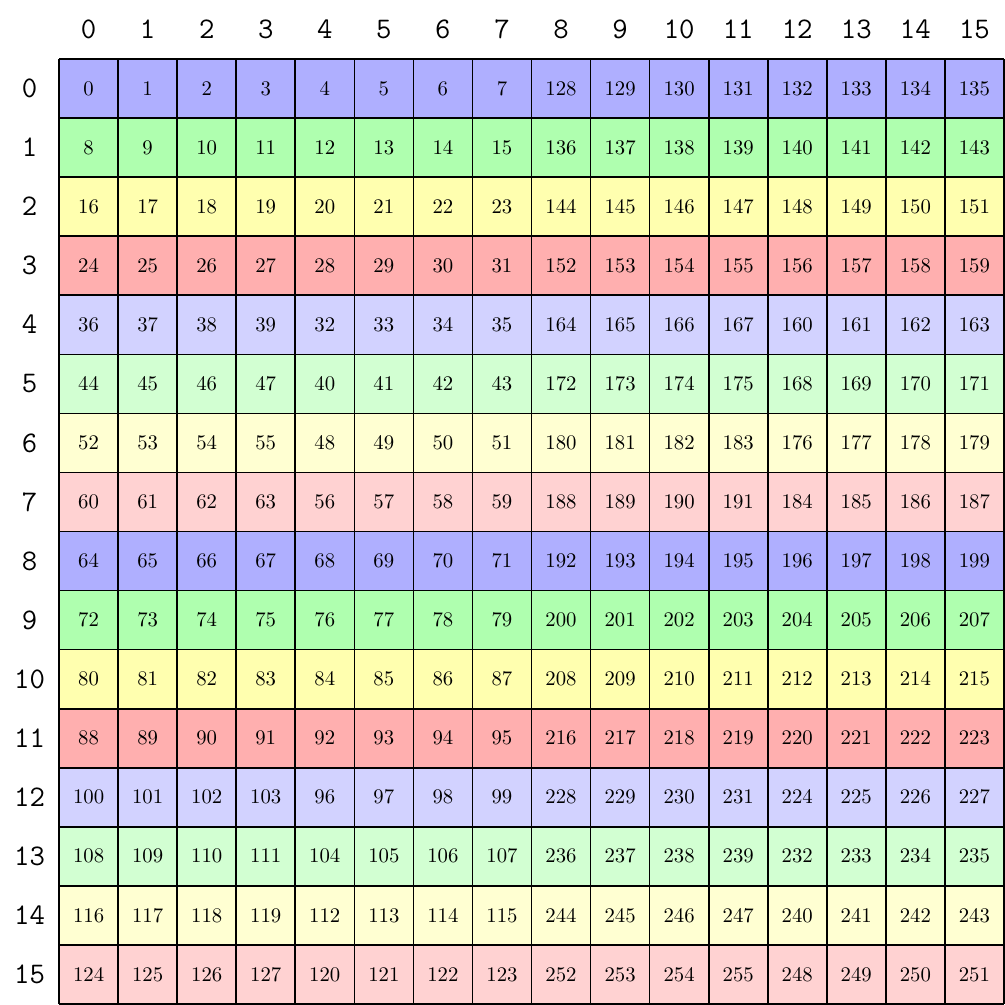

32 字节混合模式

下表显示了目标数据布局的模式,其中每个元素(编号单元格)为 16 字节,起始地址为 256 字节对齐

0

1

2

3

4

5

6

7

1

0

3

2

5

4

7

6

… 模式重复 …

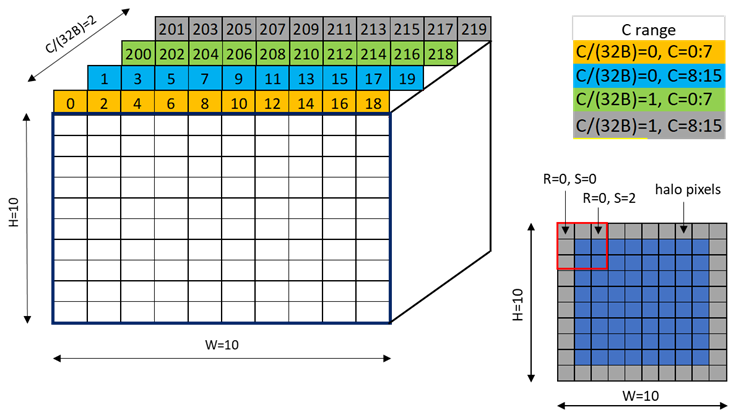

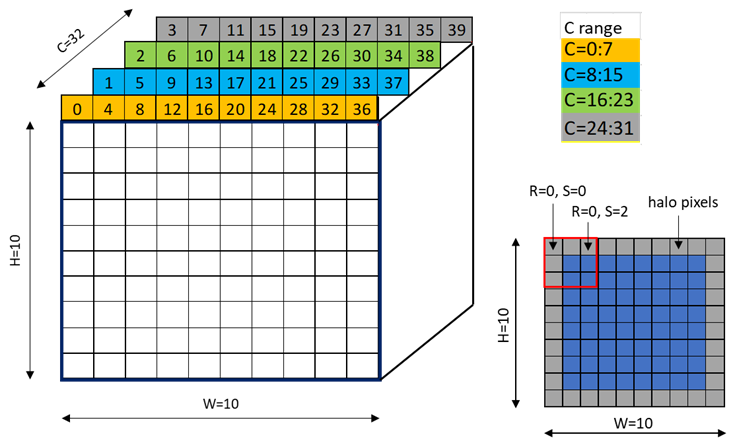

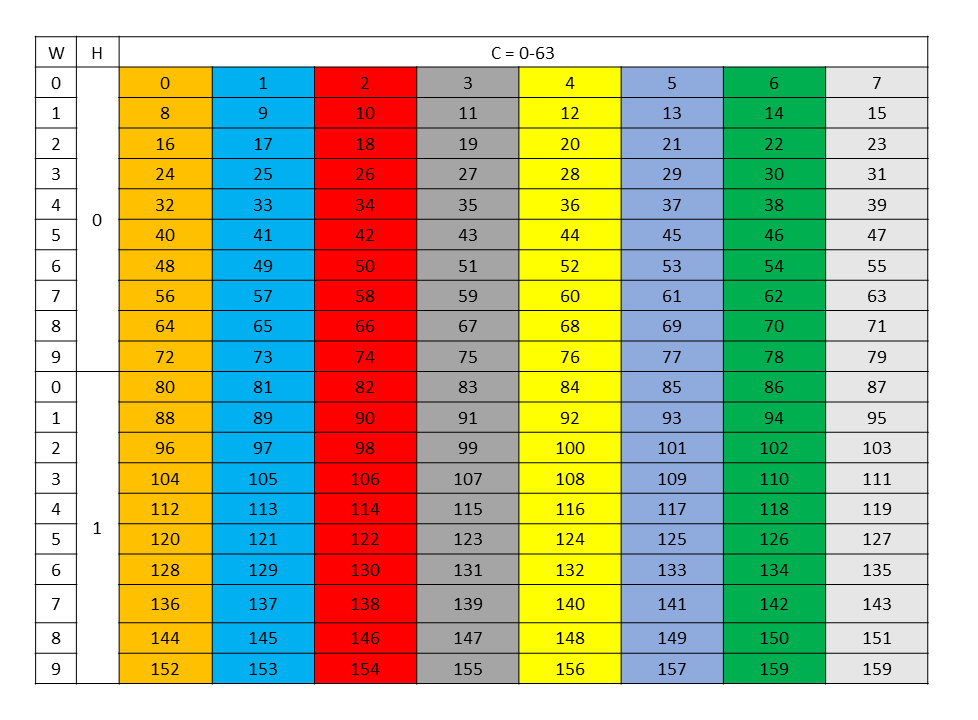

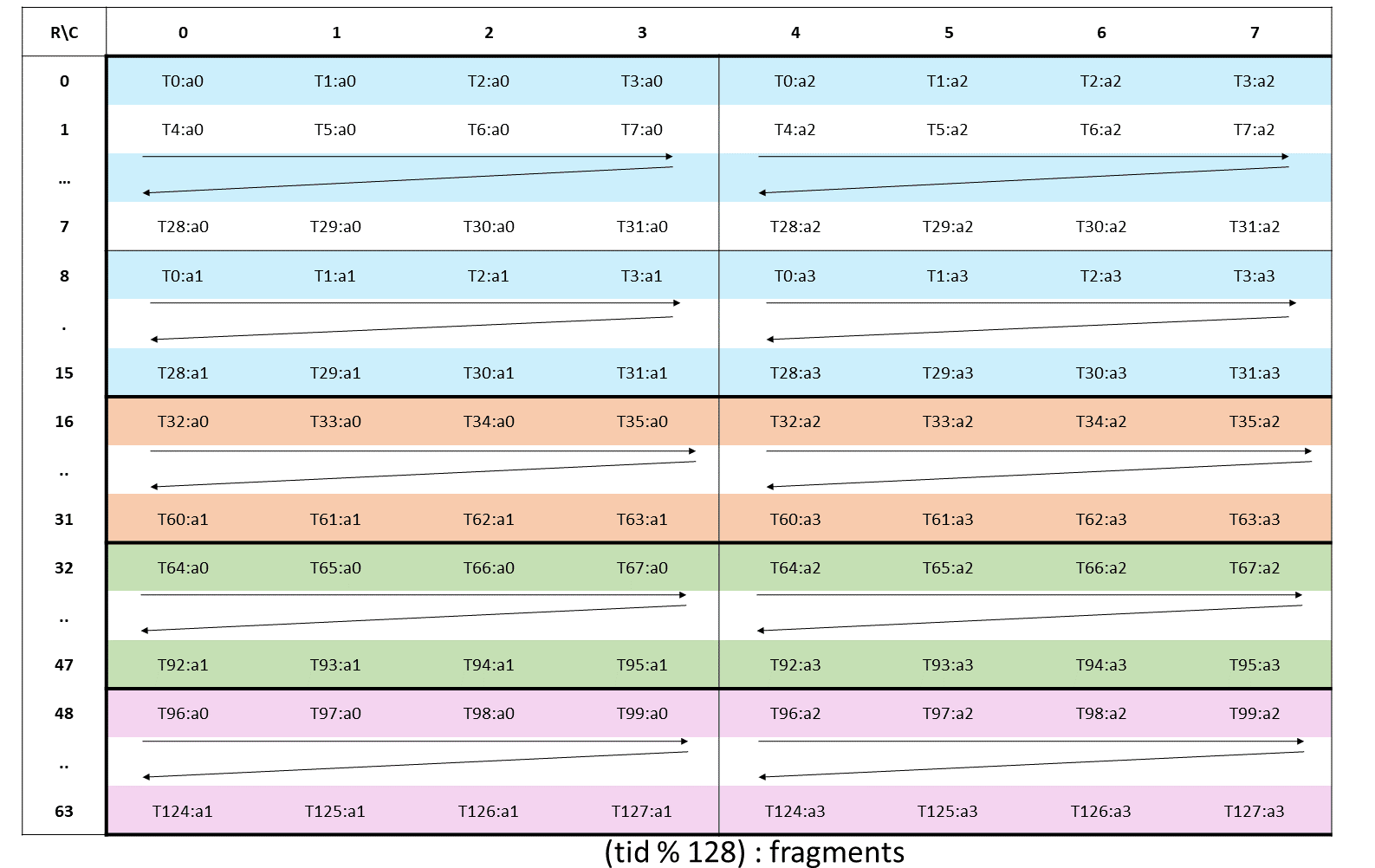

图 25 显示了维度为 1x2x10x10xC16 的 NC/(32B)HWC(32B) 张量的 32 字节混合模式示例,其中最内层维度包含 16 个通道的切片,每个通道 2 字节。

图 25 32 字节混合模式示例

图 26 显示了张量的两个片段:一个用于 C/(32B) = 0,另一个用于 C/(32B) = 1。

图 26 32 字节混合模式片段

图 27 显示了使用 32 字节混合的目标数据布局。

图 27 32 字节混合模式目标数据布局

-

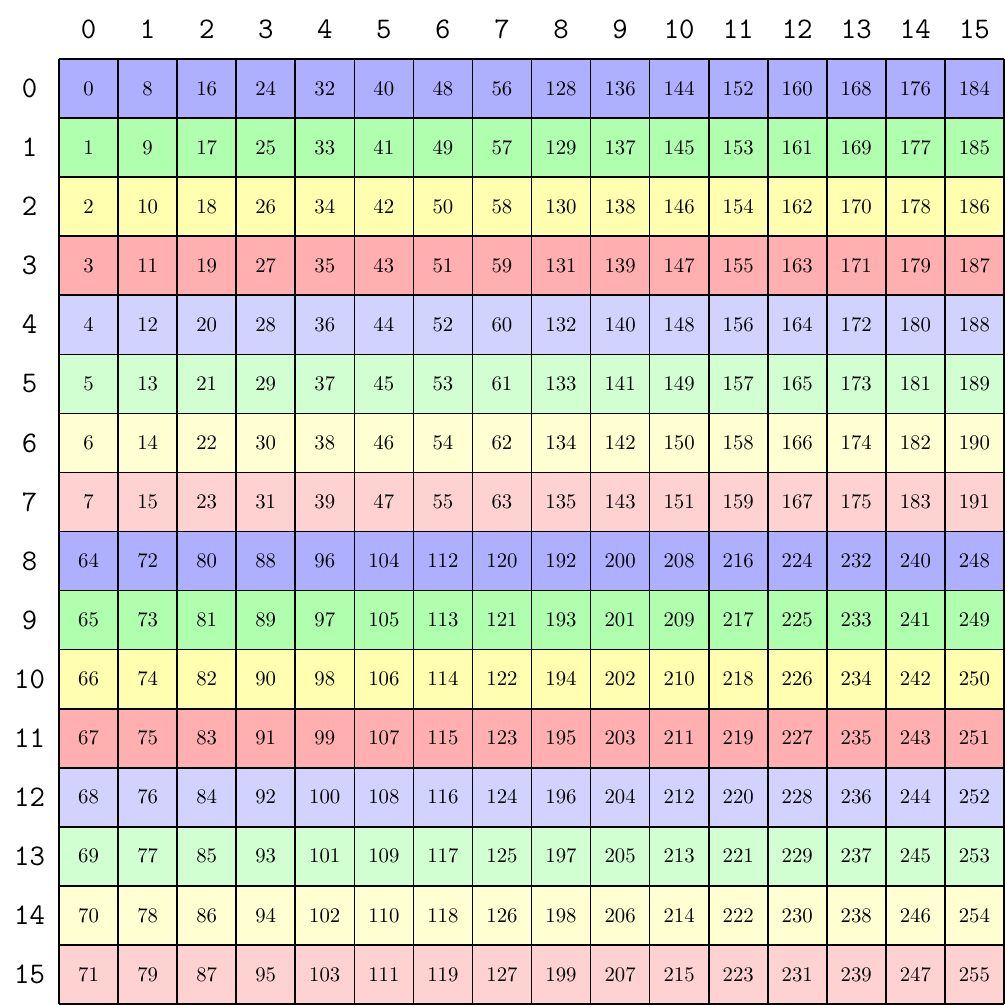

64 字节混合模式

下表显示了目标数据布局的模式,其中每个元素(编号单元格)为 16 字节,起始地址为 512 字节对齐

0

1

2

3

4

5

6

7

1

0

3

2

5

4

7

6

2

3

0

1

6

7

4

5

3

2

1

0

7

6

5

4

… 模式重复 …

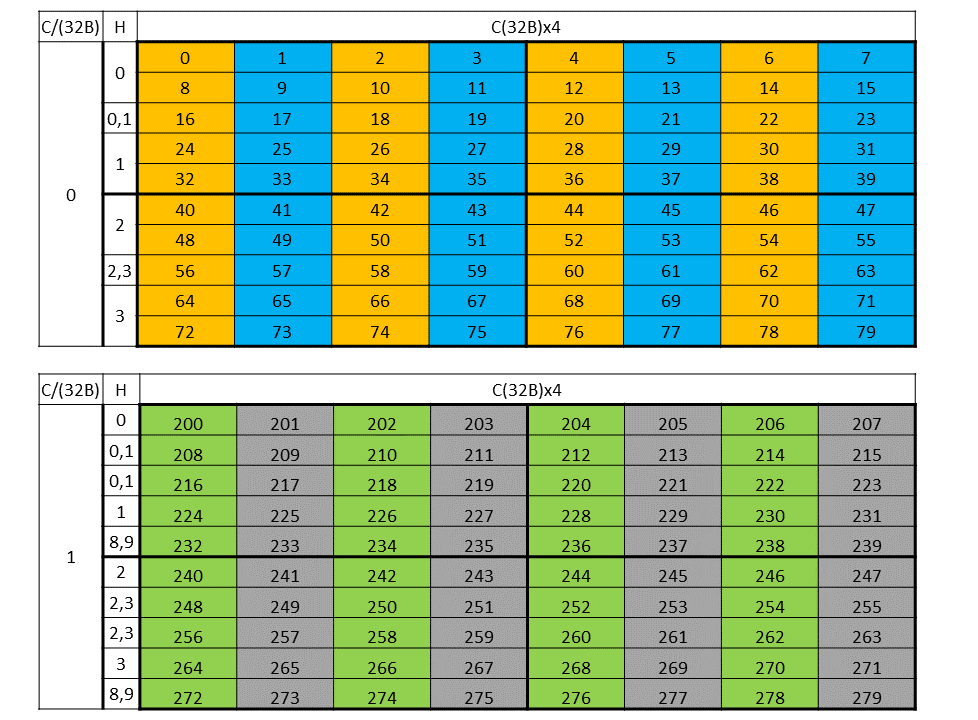

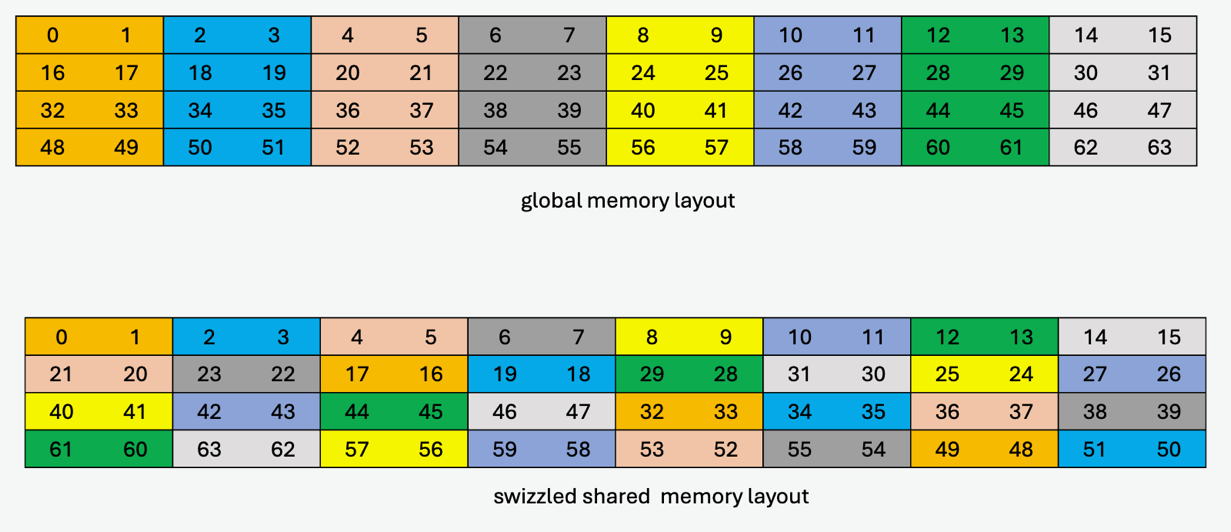

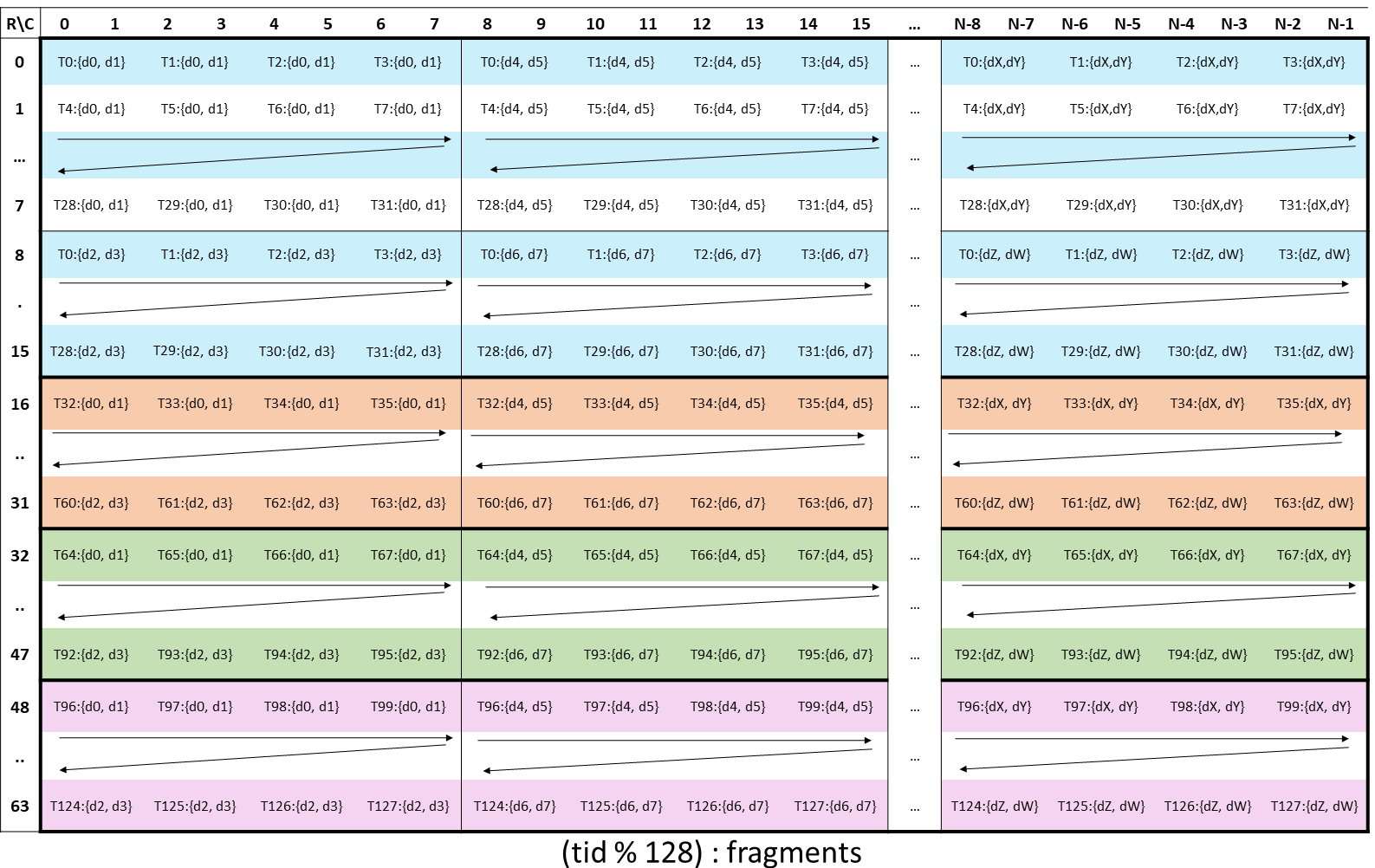

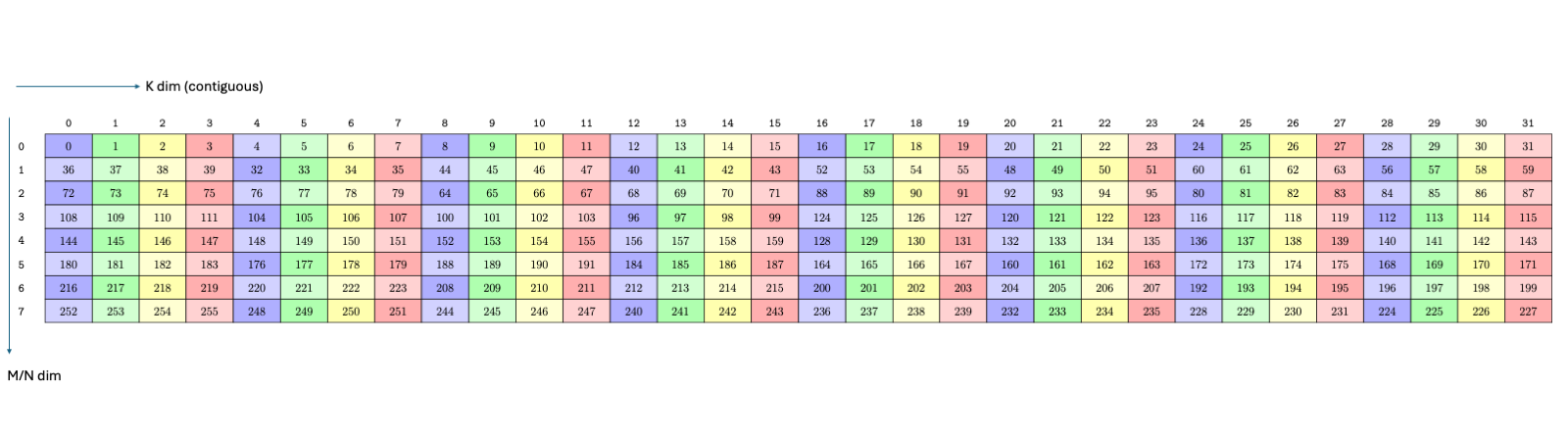

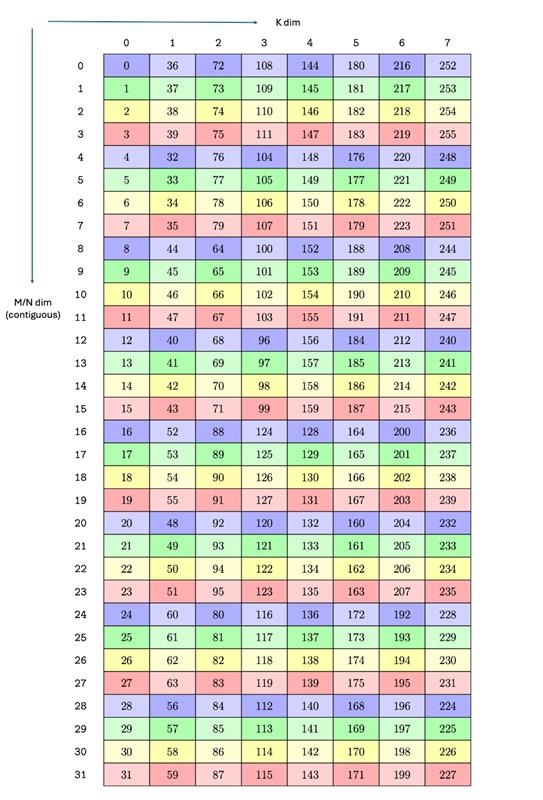

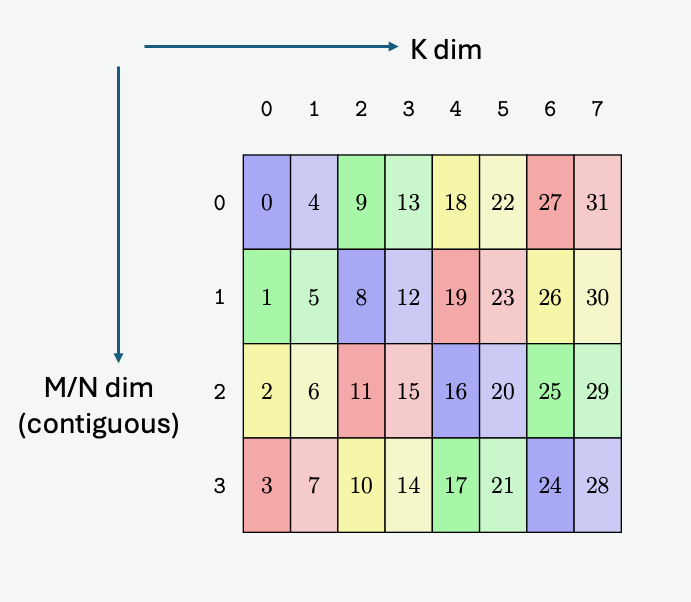

图 28 显示了维度为 1x10x10x64 的 NHWC 张量的 64 字节混合模式示例,每个通道 2 字节和 32 个通道。

图 28 64 字节混合模式示例

每个彩色单元格代表 8 个通道。图 29 显示了源数据布局。

图 29 64 字节混合模式源数据布局

图 30 显示了使用 64 字节混合的目标数据布局。

图 30 64 字节混合模式目标数据布局

-

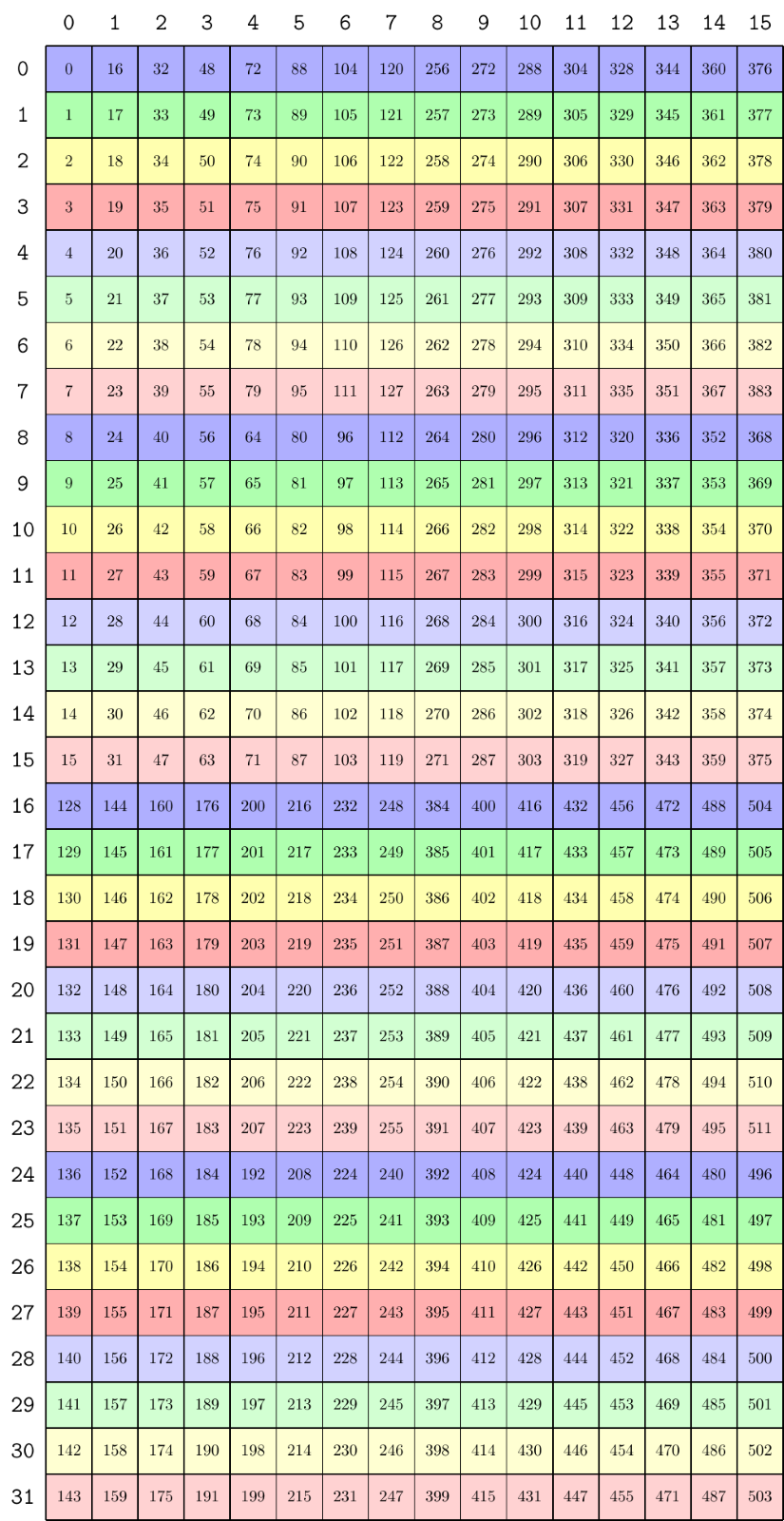

128 字节混合模式

128 字节混合模式支持以下子模式

-

16 字节原子性子模式

在此子模式下,16 字节的数据在混合时保持完整。

下表显示了目标数据布局的模式,其中每个元素(编号单元格)为 16 字节,起始地址为 1024 字节对齐

0

1

2

3

4

5

6

7

1

0

3

2

5

4

7

6

2

3

0

1

6

7

4

5

3

2

1

0

7

6

5

4

4

5

6

7

0

1

2

3

5

4

7

6

1

0

3

2

6

7

4

5

2

3

0

1

… 模式重复 …

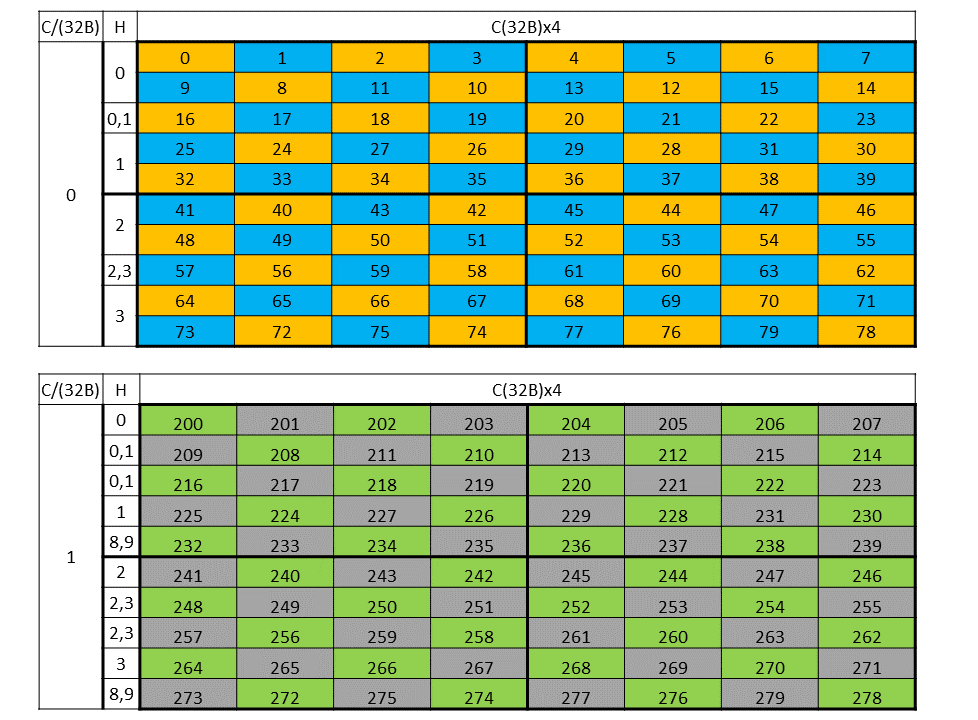

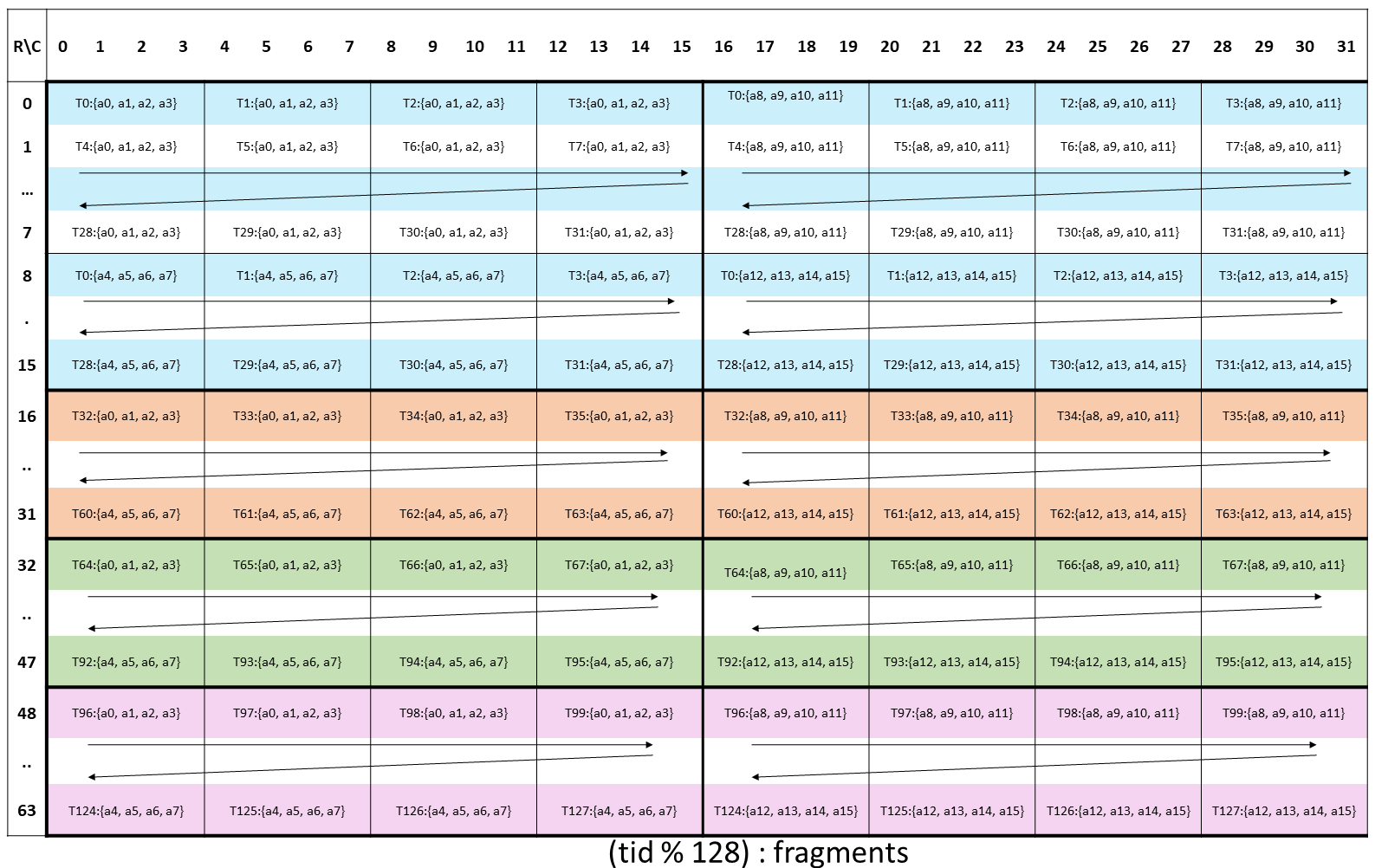

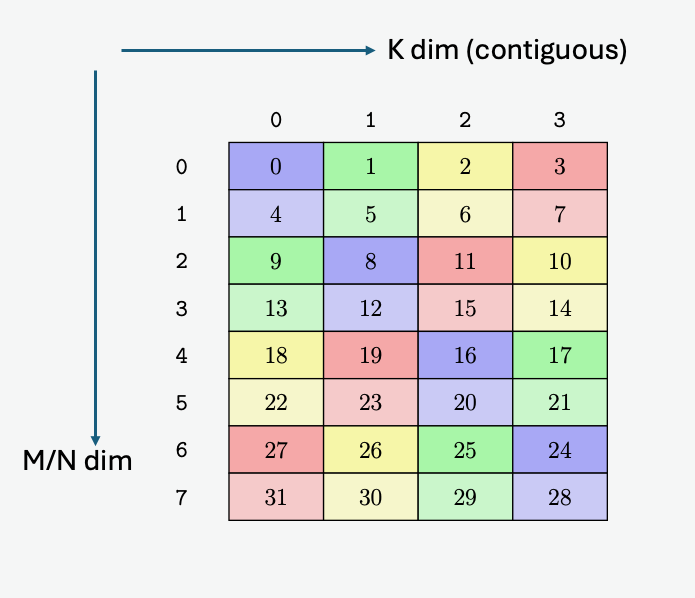

图 31 显示了维度为 1x10x10x64 的 NHWC 张量的 128 字节混合模式示例,每个通道 2 字节和 64 个通道。

图 31 128 字节混合模式示例

每个彩色单元格代表 8 个通道。图 32 显示了源数据布局。

图 32 128 字节混合模式源数据布局

图 33 显示了使用 128 字节混合的目标数据布局。

图 33 128 字节混合模式目标数据布局

-

32 字节原子性子模式

在此子模式下,32 字节的数据在混合时保持完整。

下表显示了目标数据布局中的混合模式,其中每个元素(编号单元格)为 16 字节

0 1

2 3

4 5

6 7

2 3

0 1

6 7

4 5

4 5

6 7

0 1

2 3

6 7

4 5

2 3

0 1

… 模式重复 …

此子模式需要在共享内存中进行 32 字节对齐。

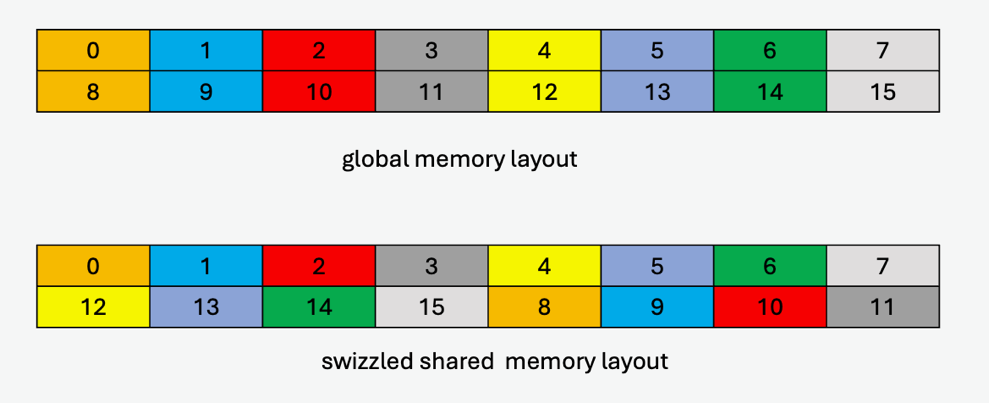

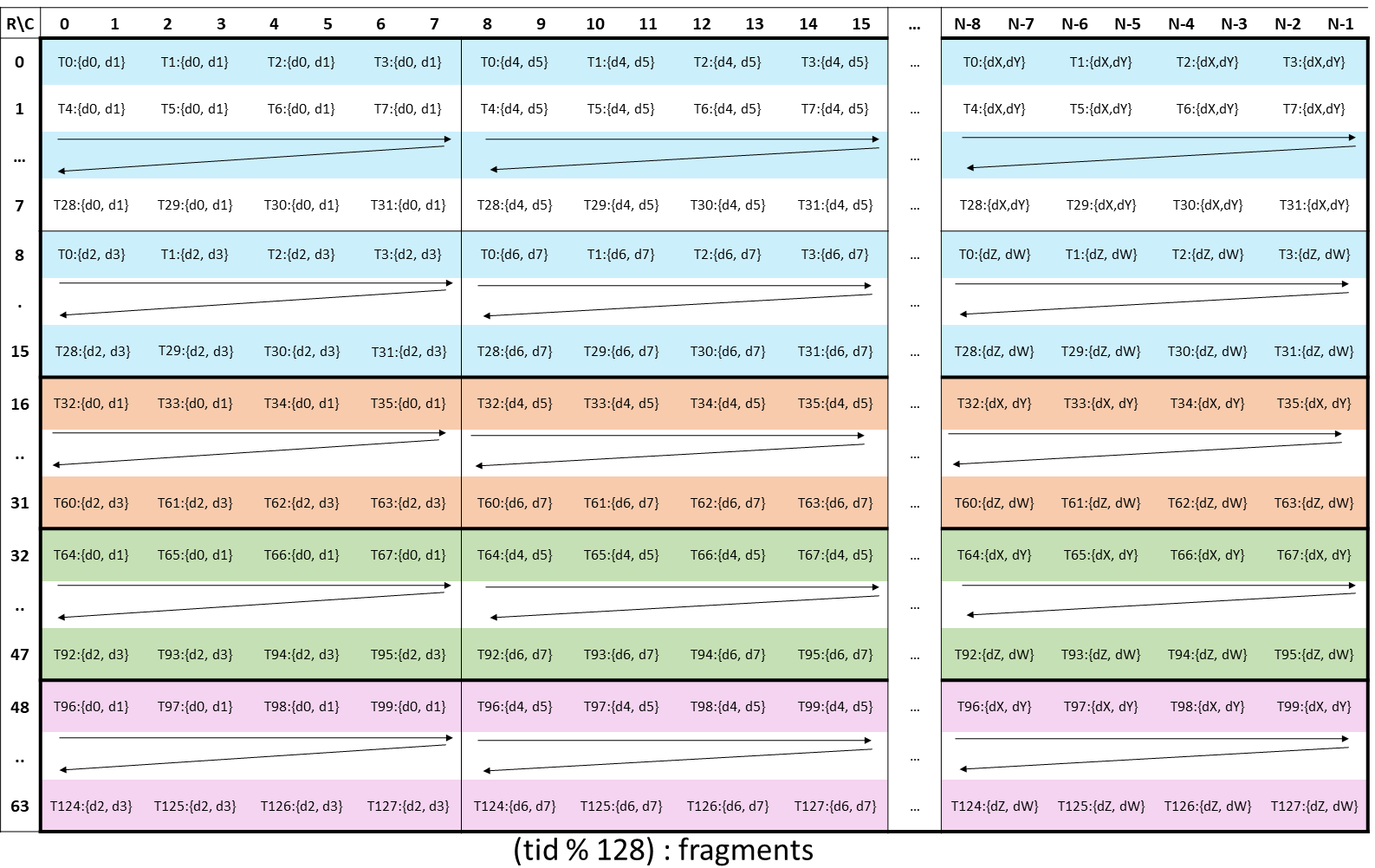

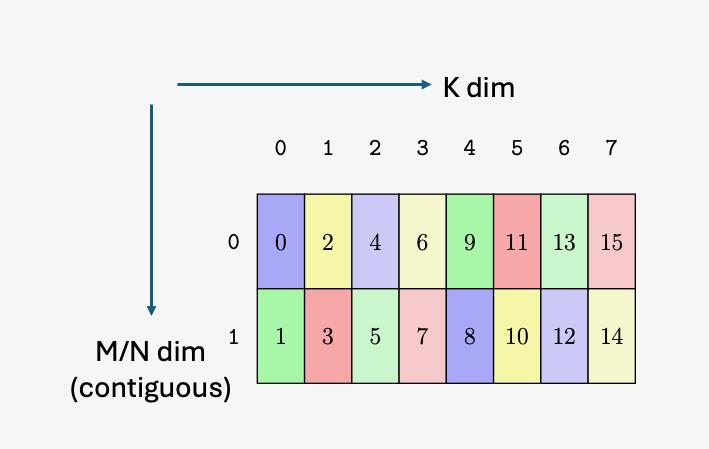

图 34 显示了全局内存中的数据布局及其在共享内存中的混合数据布局的示例,其中每个元素(彩色单元格)为 16 字节

图 34 具有 32 字节原子性的 128 字节混合模式示例

-

具有 8 字节翻转的 32 字节原子性子模式

此子模式的混合模式与 32 字节原子性子模式类似,不同之处在于在每个交替的共享内存行中,16 字节数据内有相邻 8 字节的翻转。

图 35 显示了全局内存中的数据布局及其在共享内存中的混合数据布局的示例,其中每个元素(彩色单元格)为 16 字节(显示了每个 16 字节彩色单元格的两个 8 字节子元素以显示翻转)

图 35 具有 8 字节翻转的 32 字节原子性的 128 字节混合模式示例

-

64 字节原子性子模式

在此子模式下,64 字节的数据在混合时保持完整。

下表显示了目标数据布局中的混合模式,其中每个元素(编号单元格)为 16 字节

0 1 2 3

4 5 6 7

4 5 6 7

0 1 2 3

… 模式重复 …

此子模式需要在共享内存中进行 64 字节对齐。

图 36 显示了全局内存中的数据布局及其在共享内存中的混合数据布局的示例,其中每个元素(彩色单元格)为 16 字节

图 36 具有 64 字节原子性的 128 字节混合模式示例

-

表 14 列出了混合原子性与混合模式的有效组合。

混合模式 |

混合原子性 |

|---|---|

无混合 |

– |

32B 混合模式 |

16B |

64B 混合模式 |

16B |

128B 混合模式 |

|

当 dstMem 共享内存地址位于以下边界时,混合基偏移量的值为 0

混合模式 |

重复模式的起始地址 |

|---|---|

128 字节混合 |

1024 字节边界 |

64 字节混合 |

512 字节边界 |

32 字节混合 |

256 字节边界 |

否则,混合基偏移量为非零值,使用以下公式计算

混合模式 |

公式 |

|---|---|

128 字节混合 |

基偏移量 = (dstMem / 128) % 8 |

64 字节混合 |

基偏移量 = (dstMem / 64) % 4 |

32 字节混合 |

基偏移量 = (dstMem / 32) % 2 |

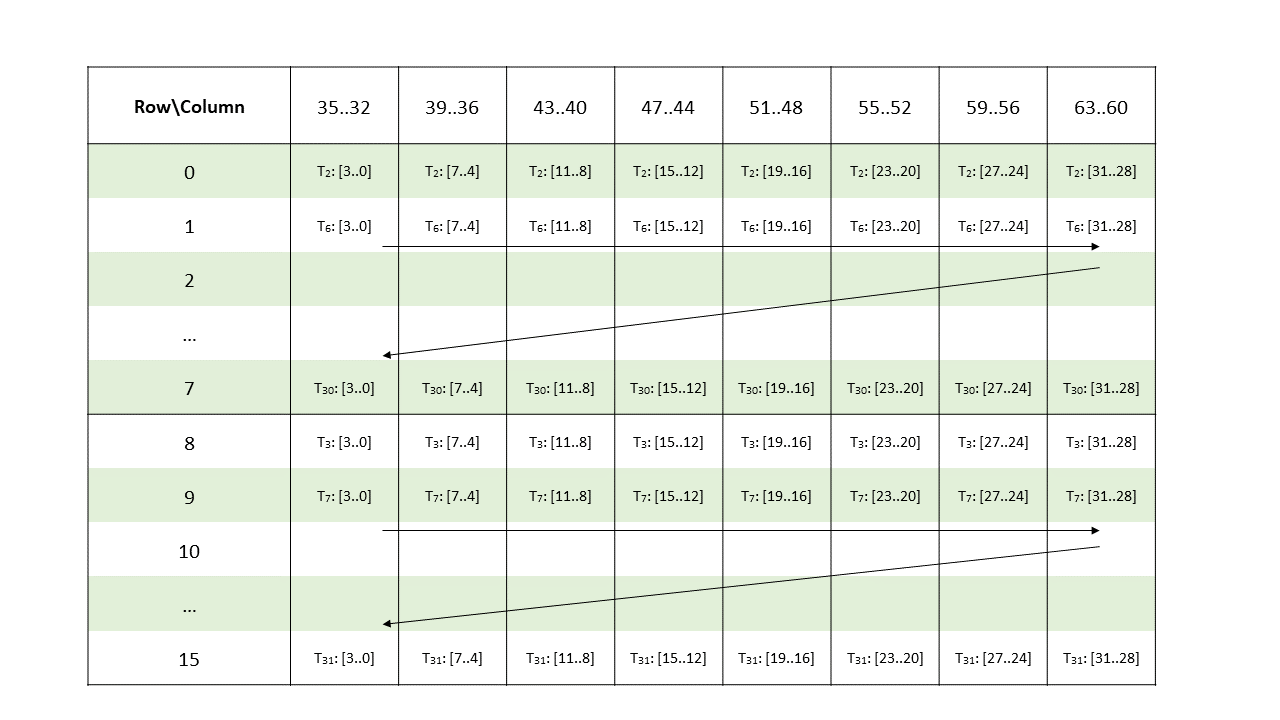

5.5.8. 张量映射

张量映射是一个 128 字节的不透明对象,位于 .const 空间、.param(内核函数参数)空间或 .global 空间中,它描述了张量属性以及前面章节中描述的张量数据的访问属性。

可以使用 CUDA API 创建张量映射。有关更多详细信息,请参阅CUDA 编程指南。

6. 指令操作数

6.1. 操作数类型信息

指令中的所有操作数都具有从其声明中已知的类型。每个操作数类型都必须与指令模板和指令类型确定的类型兼容。类型之间没有自动转换。

位大小类型与每个具有相同大小的类型兼容。公共大小的整数类型彼此兼容。类型不同但与指令类型兼容的操作数会被静默转换为指令类型。

6.2. 源操作数

源操作数在指令描述中用名称 a、b 和 c 表示。PTX 描述了一个加载-存储机器,因此 ALU 指令的操作数都必须在 .reg 寄存器状态空间中声明的变量中。对于大多数操作,操作数的大小必须一致。

cvt(转换)指令采用各种操作数类型和大小,因为它的工作是将几乎任何数据类型转换为任何其他数据类型(和大小)。

ld、st、mov 和 cvt 指令将数据从一个位置复制到另一个位置。ld 和 st 指令将数据从/到可寻址状态空间移动到/从寄存器。mov 指令在寄存器之间复制数据。

大多数指令都有一个可选的谓词保护,用于控制条件执行,少数指令还有额外的谓词源操作数。谓词操作数用名称 p、q、r、s 表示。

6.3. 目标操作数

生成单个结果的 PTX 指令将结果存储在指令描述中用 d(代表目标)表示的字段中。结果操作数是寄存器状态空间中的标量或向量变量。

6.4. 使用地址、数组和向量

使用标量变量作为操作数很简单。有趣的功能始于地址、数组和向量。

6.4.1. 地址作为操作数

所有内存指令都采用地址操作数,该操作数指定要访问的内存位置。此可寻址操作数是以下之一

[var]-

可寻址变量

var的名称。 [reg]-

包含字节地址的整数或位大小类型寄存器

reg。 [reg+immOff]-

寄存器

reg(包含字节地址)与常量整数字节偏移量(有符号,32 位)的总和。 [var+immOff]-

可寻址变量

var的地址(包含字节地址)与常量整数字节偏移量(有符号,32 位)的总和。 [immAddr]-

立即绝对字节地址(无符号,32 位)。

var[immOff]-

如数组作为操作数中所述的数组元素。

包含地址的寄存器可以声明为位大小类型或整数类型。

内存指令的访问大小是在内存中访问的总字节数。例如,ld.v4.b32 的访问大小为 16 字节,而 atom.f16x2 的访问大小为 4 字节。

地址必须自然对齐到访问大小的倍数。如果地址未正确对齐,则结果行为未定义。例如,除其他事项外,访问可能会通过静默屏蔽低位地址位以实现适当的舍入来继续,或者指令可能会出错。

地址大小可以是 32 位或 64 位。不支持 128 位地址。地址根据需要零扩展到指定的宽度,如果寄存器宽度超过目标体系结构的状态空间地址宽度,则会截断地址。

地址算术使用整数算术和逻辑指令执行。示例包括指针算术和指针比较。所有地址和地址计算都是基于字节的;不支持 C 风格的指针算术。

mov 指令可用于将变量的地址移动到指针中。该地址是变量声明所在状态空间中的偏移量。加载和存储操作在寄存器和可寻址状态空间中的位置之间移动数据。语法类似于许多汇编语言中使用的语法,其中标量变量只是简单地命名,地址通过将地址表达式括在方括号中来取消引用。地址表达式包括变量名、地址寄存器、地址寄存器加字节偏移量,以及在编译时评估为常量地址的立即地址表达式。

以下是一些示例

.shared .u16 x;

.reg .u16 r0;

.global .v4 .f32 V;

.reg .v4 .f32 W;

.const .s32 tbl[256];

.reg .b32 p;

.reg .s32 q;

ld.shared.u16 r0,[x];

ld.global.v4.f32 W, [V];

ld.const.s32 q, [tbl+12];

mov.u32 p, tbl;

6.4.1.1. 通用寻址

如果内存指令未指定状态空间,则使用通用寻址执行操作。状态空间 .const、内核函数参数 (.param)、.local 和 .shared 被建模为通用地址空间内的窗口。每个窗口由窗口基址和窗口大小定义,窗口大小等于相应状态空间的大小。除非通用地址落在 const、local 或 shared 内存的窗口内,否则通用地址将映射到 global 内存。内核函数参数 (.param) 窗口包含在 .global 窗口内。在每个窗口内,通用地址通过从通用地址中减去窗口基址来映射到基础状态空间中的地址。

6.4.2. 数组作为操作数

可以声明所有类型的数组,并且标识符成为数组声明空间中的地址常量。数组的大小是程序中的常量。

可以使用显式计算的字节地址访问数组元素,也可以使用方括号表示法索引到数组中。方括号内的表达式可以是常量整数、寄存器变量或简单的寄存器加常量偏移量表达式,其中偏移量是从寄存器变量加或减的常量表达式。如果需要更复杂的索引,则必须在使用前将其编写为地址计算。例如

ld.global.u32 s, a[0];

ld.global.u32 s, a[N-1];

mov.u32 s, a[1]; // move address of a[1] into s

6.4.3. 向量作为操作数

向量操作数受指令的有限子集支持,其中包括 mov、ld、st、atom、red 和 tex。向量也可以作为参数传递给调用的函数。

可以使用后缀 .x、.y、.z 和 .w 以及典型的颜色字段 .r、.g、.b 和 .a 从向量中提取向量元素。

花括号括起来的列表用于模式匹配以分解向量。

.reg .v4 .f32 V;

.reg .f32 a, b, c, d;

mov.v4.f32 {a,b,c,d}, V;

向量加载和存储可用于实现宽加载和存储,这可以提高内存性能。加载/存储操作中的寄存器可以是向量,也可以是花括号括起来的类似类型的标量列表。以下是一些示例

ld.global.v4.f32 {a,b,c,d}, [addr+16];

ld.global.v2.u32 V2, [addr+8];

花括号括起来的向量中的元素,例如 {Ra, Rb, Rc, Rd},对应于提取的元素,如下所示

Ra = V.x = V.r

Rb = V.y = V.g

Rc = V.z = V.b

Rd = V.w = V.a

6.4.4. 标签和函数名称作为操作数

标签和函数名称只能分别在 bra/brx.idx 和 call 指令中使用。函数名称可以在 mov 指令中使用,以获取函数地址到寄存器中,以便在间接调用中使用。

从 PTX ISA 版本 3.1 开始,mov 指令可用于获取内核函数的地址,以便传递给启动 GPU 内核调用的系统调用。此功能是 CUDA 动态并行性支持的一部分。有关详细信息,请参阅CUDA 动态并行性编程指南。

6.5. 类型转换

所有算术、逻辑和数据移动指令的所有操作数必须具有相同的类型和大小,除了更改大小和/或类型是指令定义的一部分的操作。不同大小或类型的操作数必须在操作之前进行转换。

6.5.1. 标量转换

表 15 显示了给定不同类型的操作数时,cvt 指令使用的精度和格式。例如,如果 cvt.s32.u16 指令被赋予 u16 源操作数和 s32 作为目标操作数,则 u16 将零扩展为 s32。

超出浮点数范围的浮点转换用最大浮点值表示(f32 和 f64 的 IEEE 754 Inf,以及 f16 的约 131,000)。

目标格式 |

||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

s8 |

s16 |

s32 |

s64 |

u8 |

u16 |

u32 |

u64 |

f16 |

f32 |

f64 |

||

源格式 |

s8 |

– |

sext |

sext |

sext |

– |

sext |

sext |

sext |

s2f |

s2f |

s2f |

s16 |

chop1 |

– |

sext |

sext |

chop1 |

– |

sext |

sext |

s2f |

s2f |

s2f |

|

s32 |

chop1 |

chop1 |

– |

sext |

chop1 |

chop1 |

– |

sext |

s2f |

s2f |

s2f |

|

s64 |

chop1 |

chop1 |

chop |

– |

chop1 |

chop1 |

chop |

– |

s2f |

s2f |

s2f |

|

u8 |

– |

zext |

zext |

zext |

– |

zext |

zext |

zext |

u2f |

u2f |

u2f |

|

u16 |

chop1 |

– |

zext |

zext |

chop1 |

– |

zext |

zext |

u2f |

u2f |

u2f |

|

u32 |

chop1 |

chop1 |

– |

zext |

chop1 |

chop1 |

– |

zext |

u2f |

u2f |

u2f |

|

u64 |

chop1 |

chop1 |

chop |

– |

chop1 |

chop1 |

chop |

– |

u2f |

u2f |

u2f |

|

f16 |

f2s |

f2s |

f2s |

f2s |

f2u |

f2u |

f2u |

f2u |

– |

f2f |

f2f |

|

f32 |

f2s |

f2s |

f2s |

f2s |

f2u |

f2u |

f2u |

f2u |

f2f |

– |

f2f |

|

f64 |

f2s |

f2s |

f2s |

f2s |

f2u |

f2u |

f2u |

f2u |

f2f |

f2f |

– |

|

注释 |

sext = 符号扩展;zext = 零扩展;chop = 仅保留低位以适应; s2f = 有符号数转浮点数;f2s = 浮点数转有符号数;u2f = 无符号数转浮点数; f2u = 浮点数转无符号数;f2f = 浮点数转浮点数。 1 如果目标寄存器比目标格式更宽,则在截断后,结果会扩展到目标寄存器宽度。扩展类型(符号或零)基于目标格式。例如,cvt.s16.u32 定向到 32 位寄存器,首先截断为 16 位,然后符号扩展为 32 位。 |

|||||||||||

6.5.2. 舍入修饰符

转换指令可以指定舍入修饰符。在 PTX 中,有四种整数舍入修饰符和四种浮点舍入修饰符。表 16 和 表 17 总结了舍入修饰符。

修饰符 |

描述 |

|---|---|

|

尾数 LSB 四舍五入到最接近的偶数 |

|

尾数 LSB 四舍五入到最接近的值,远离零 |

|

尾数 LSB 向零舍入 |

|

尾数 LSB 向负无穷大舍入 |

|

尾数 LSB 向正无穷大舍入 |

修饰符 |

描述 |

|---|---|

|

四舍五入到最接近的整数,如果源介于两个整数之间,则选择偶数整数。 |

|

向零方向舍入到最接近的整数 |

|

向负无穷大方向舍入到最接近的整数 |

|

向正无穷大方向舍入到最接近的整数 |

6.6. 操作数成本

来自不同状态空间的操作数会影响操作的速度。寄存器最快,而全局内存最慢。内存延迟的大部分可以通过多种方式隐藏。第一种方式是拥有多个执行线程,以便硬件可以发出内存操作,然后切换到其他执行。另一种隐藏延迟的方法是尽早发出加载指令,因为执行不会被阻塞,直到在后续(时间上)指令中使用所需的结果。存储操作中的寄存器可以更快地可用。表 18 给出了访问不同类型内存的成本估算。

空间 |

时间 |

注释 |

|---|---|---|

寄存器 |

0 |

|

共享 |

0 |

|

常量 |

0 |

分摊成本低,首次访问成本高 |

本地 |

> 100 个时钟周期 |

|

参数 |

0 |

|

立即数 |

0 |

|

全局 |

> 100 个时钟周期 |

|

纹理 |

> 100 个时钟周期 |

|

表面 |

> 100 个时钟周期 |

7. 抽象 ABI

PTX 没有暴露特定调用约定、堆栈布局和应用程序二进制接口 (ABI) 的细节,而是提供了一个稍高级别的抽象,并支持多种 ABI 实现。在本节中,我们将描述实现 ABI 隐藏所需的 PTX 功能。这些功能包括函数定义、函数调用、参数传递、对可变参数函数(varargs)的支持以及在堆栈上分配的内存(alloca)。

有关生成符合 CUDA® 架构的应用程序二进制接口 (ABI) 的 PTX 的详细信息,请参阅PTX Writers Guide to Interoperability。

7.1. 函数声明和定义

在 PTX 中,函数使用 .func 指令声明和定义。函数声明指定一个可选的返回参数列表、函数名称和一个可选的输入参数列表;这些共同指定了函数的接口或原型。函数定义指定了函数的接口和函数体。函数必须在被调用之前声明或定义。

最简单的函数没有参数或返回值,在 PTX 中表示如下

.func foo

{

...

ret;

}

...

call foo;

...

在这里,call 指令的执行将控制权转移到 foo,隐式保存返回地址。foo 内 ret 指令的执行将控制权转移到调用之后的指令。

标量和向量基本类型输入和返回参数可以简单地表示为寄存器变量。在调用时,参数可以是寄存器变量或常量,返回值可以直接放入寄存器变量中。调用时的参数和返回变量必须具有与被调用者的相应形式参数匹配的类型和大小。

例子

.func (.reg .u32 %res) inc_ptr ( .reg .u32 %ptr, .reg .u32 %inc )

{

add.u32 %res, %ptr, %inc;

ret;

}

...

call (%r1), inc_ptr, (%r1,4);

...

当使用 ABI 时,.reg 状态空间参数的大小必须至少为 32 位。源语言中的子字标量对象应在 PTX 中提升为 32 位寄存器,或者使用接下来描述的 .param 状态空间字节数组。

诸如 C 结构和联合之类的对象在 PTX 中被展平为寄存器或字节数组,并使用 .param 空间内存表示。例如,考虑以下 C 结构,通过值传递给函数

struct {

double dbl;

char c[4];

};

在 PTX 中,此结构将被展平为字节数组。由于内存访问需要与访问大小的倍数对齐,因此本例中的结构将是一个 12 字节的数组,具有 8 字节对齐,以便对 .f64 字段的访问是对齐的。.param 状态空间用于按值传递结构

例子

.func (.reg .s32 out) bar (.reg .s32 x, .param .align 8 .b8 y[12])

{

.reg .f64 f1;

.reg .b32 c1, c2, c3, c4;

...

ld.param.f64 f1, [y+0];

ld.param.b8 c1, [y+8];

ld.param.b8 c2, [y+9];

ld.param.b8 c3, [y+10];

ld.param.b8 c4, [y+11];

...

... // computation using x,f1,c1,c2,c3,c4;

}

{

.param .b8 .align 8 py[12];

...

st.param.b64 [py+ 0], %rd;

st.param.b8 [py+ 8], %rc1;

st.param.b8 [py+ 9], %rc2;

st.param.b8 [py+10], %rc1;

st.param.b8 [py+11], %rc2;

// scalar args in .reg space, byte array in .param space

call (%out), bar, (%x, py);

...

在本例中,请注意 .param 空间变量以两种方式使用。首先,.param 变量 y 在函数定义 bar 中用于表示形式参数。其次,.param 变量 py 在调用函数的正文中声明,并用于设置要传递给 bar 的结构。

以下是思考设备函数中 .param 状态空间使用情况的概念方式。

对于调用者,

.param状态空间用于设置将传递给被调用函数的值和/或接收来自被调用函数的返回值。通常,.param字节数组用于将按值传递的结构的字段收集在一起。

对于被调用者,

.param状态空间用于接收参数值和/或将返回值传递回调用者。

以下限制适用于参数传递。

对于调用者,

参数可以是

.param变量、.reg变量或常量。在作为字节数组的

.param空间形式参数的情况下,参数也必须是具有匹配类型、大小和对齐方式的.param空间字节数组。.param参数必须在调用者的本地作用域内声明。在作为基本类型标量或向量变量的

.param空间形式参数的情况下,相应的参数可以是具有匹配类型和大小的.param或.reg空间变量,也可以是可以用形式参数类型表示的常量。在

.reg空间形式参数的情况下,相应的参数可以是具有匹配类型和大小的.param或.reg空间变量,也可以是可以用形式参数类型表示的常量。在

.reg空间形式参数的情况下,寄存器的大小必须至少为 32 位。用于将参数传递给函数调用的所有

st.param指令都必须紧接在相应的call指令之前,并且用于收集返回值的ld.param指令必须紧接在call指令之后,且没有任何控制流更改。用于参数传递的st.param和ld.param指令不能被谓词化。这使得编译器优化成为可能,并确保.param变量不会在调用者的帧中消耗超出 ABI 所需的额外空间。.param变量仅允许在调用站点建立数据之间的映射(例如,调用者操作的结构位于寄存器和内存中),以便可以作为参数或返回值传递给被调用者。

对于被调用者,

输入和返回参数可以是

.param变量或.reg变量。.param内存中的参数必须与 1、2、4、8 或 16 字节的倍数对齐。.reg状态空间中的参数的大小必须至少为 32 位。.reg状态空间可用于接收和返回基本类型标量和向量值,包括在非 ABI 模式下编译时的子字大小对象。支持.reg状态空间提供遗留支持。

请注意,选择 .reg 或 .param 状态空间用于参数传递对参数最终是在物理寄存器还是堆栈中传递没有影响。参数到物理寄存器和堆栈位置的映射取决于 ABI 定义以及参数的顺序、大小和对齐方式。

7.1.1. PTX ISA 版本 1.x 的变更

在 PTX ISA 版本 1.x 中,形式参数被限制为 .reg 状态空间,并且不支持数组参数。诸如 C 结构之类的对象被展平并使用多个寄存器传递或返回。PTX ISA 版本 1.x 为此目的支持多个返回值。

从 PTX ISA 版本 2.0 开始,形式参数可以在 .reg 或 .param 状态空间中,并且 .param 空间参数支持数组。对于 sm_20 或更高版本的目标,PTX 将函数限制为单个返回值,并且 .param 字节数组应用于返回不适合寄存器的对象。PTX 继续为 sm_1x 目标支持多个返回寄存器。

注意

PTX 仅为 sm_20 或更高版本的目标实现基于堆栈的 ABI。

PTX ISA 3.0 之前的版本允许在模块作用域中定义 .reg 和 .local 状态空间中的变量。当编译为使用 ABI 时,PTX ISA 版本 3.0 及更高版本不允许模块作用域的 .reg 和 .local 变量,并将它们的使用限制在函数作用域内。当在不使用 ABI 的情况下编译时,模块作用域的 .reg 和 .local 变量像以前一样受到支持。当编译包含模块作用域的 .reg 或 .local 变量的旧版 PTX 代码(ISA 版本 3.0 之前)时,编译器会静默禁用 ABI 的使用。

7.2. 可变参数函数

注意

对未实现的可变参数函数的支持已从规范中删除。

PTX 版本 6.0 支持将未调整大小的数组参数传递给函数,该函数可用于实现可变参数函数。

有关详细信息,请参阅 内核和函数指令:.func

7.3. Alloca

PTX 提供了 alloca 指令,用于在运行时在每个线程的本地内存堆栈上分配存储空间。可以使用 ld.local 和 st.local 指令,使用 alloca 返回的指针访问分配的堆栈内存。

为了方便释放使用 alloca 分配的内存,PTX 提供了两个额外的指令:stacksave,它允许读取局部变量中堆栈指针的值,以及 stackrestore,它可以使用保存的值恢复堆栈指针。

alloca、stacksave 和 stackrestore 指令在 堆栈操作指令 中描述。

- 预览功能

-

堆栈操作指令

alloca、stacksave和stackrestore是 PTX ISA 版本 7.3 中的预览功能。所有详细信息如有更改,恕不另行通知,并且在未来的 PTX ISA 版本或 SM 架构上不保证向后兼容性。

8. 内存一致性模型

在多线程执行中,每个线程执行的内存操作的副作用以部分且非相同的顺序对其他线程可见。这意味着任何两个操作对于不同的线程可能看起来没有顺序,或者顺序不同。内存一致性模型引入的公理精确地指定了不同线程观察到的顺序之间禁止哪些矛盾。

在没有任何约束的情况下,每个读取操作都会返回由某个写入操作提交到同一内存位置的值,包括对该内存位置的初始写入。内存一致性模型有效地约束了读取操作可以从中返回值的一组此类候选写入。

8.1. 模型的范围和适用性

本模型下指定的约束适用于任何 PTX ISA 版本号的 PTX 程序,这些程序在 sm_70 或更高版本的架构上运行。

内存一致性模型不适用于纹理(包括 ld.global.nc)和表面访问。

8.1.1. 系统范围内原子性的限制

当与主机 CPU 通信时,某些具有系统范围的强操作在某些系统上可能无法原子地执行。有关主机内存原子性保证的更多详细信息,请参阅CUDA Atomicity Requirements。

8.2. 内存操作

PTX 内存模型中的基本存储单元是一个字节,由 8 位组成。PTX 程序可用的每个状态空间都是内存中连续字节的序列。PTX 状态空间中的每个字节都有一个相对于可以访问同一状态空间的所有线程的唯一地址。

每个 PTX 内存指令都指定一个地址操作数和一个数据类型。地址操作数包含一个虚拟地址,该虚拟地址在内存访问期间转换为物理地址。物理地址和数据类型的大小共同定义了一个物理内存位置,该位置是从物理地址开始并扩展到数据类型大小(以字节为单位)的字节范围。

内存一致性模型规范使用术语“地址”或“内存地址”来指示虚拟地址,并使用术语“内存位置”来指示物理内存位置。

每个 PTX 内存指令还指定要对相应内存位置中的所有字节执行的操作 - 读取、写入或原子读-修改-写。

8.2.1. 重叠

当一个位置的起始地址在构成另一个位置的字节范围内时,两个内存位置被称为重叠。当两个内存操作指定相同的虚拟地址并且相应的内存位置重叠时,这两个内存操作被称为重叠。当两个内存位置相同时,重叠被称为完全重叠,否则被称为部分重叠。

8.2.2. 别名

如果两个不同的虚拟地址映射到同一个内存位置,则称它们为别名。

8.2.3. 多内存地址

多内存地址是一个虚拟地址,它指向跨设备的多个不同内存位置。

只有 multimem.* 操作在多内存地址上有效。也就是说,在任何其他内存操作中访问多内存地址的行为是未定义的。

8.2.4. 向量数据类型上的内存操作

内存一致性模型将对内存位置执行的操作与标量数据类型相关联,标量数据类型的最大大小和对齐方式为 64 位。向量数据类型的内存操作被建模为一组等效的标量数据类型的内存操作,这些操作以未指定的顺序在向量中的元素上执行。

8.2.5. 打包数据类型上的内存操作

打包数据类型由两个相同标量数据类型的值组成,如 打包数据类型 中所述。这些值在相邻的内存位置中访问。打包数据类型上的内存操作被建模为一对等效的标量数据类型的内存操作,这些操作以未指定的顺序在打包数据的每个元素上执行。

8.2.6. 初始化

内存中的每个字节都由假设的写入 W0 初始化,W0 在程序中启动任何线程之前执行。如果字节包含在程序变量中,并且该变量具有初始值,则 W0 为该字节写入相应的初始值;否则,W0 被假定为已将未知但恒定的值写入该字节。

8.3. 状态空间

内存一致性模型中定义的关系独立于状态空间。特别是,因果关系闭合了所有状态空间中的所有内存操作。但是,只有一个状态空间中的内存操作的副作用才能被同样可以访问同一状态空间的操作直接观察到。这进一步约束了除了范围之外的内存操作的同步效果。例如,PTX 指令 ld.relaxed.shared.sys 的同步效果与 ld.relaxed.shared.cluster 的同步效果相同,因为同一集群之外的线程都无法执行访问同一内存位置的操作。

8.4. 操作类型

为简单起见,文档的其余部分引用以下操作类型,而不是提及产生这些操作的特定指令。

操作类型 |

指令/操作 |

|---|---|

原子操作 |

|

读取操作 |

|

写入操作 |

|

内存操作 |

读取或写入操作。 |

易失性操作 |

带有 |

获取操作 |

带有 |

释放操作 |

带有 |

mmio 操作 |

带有 |

内存屏障操作 |

|

代理屏障操作 |

|

强操作 |

内存屏障操作,或带有 |

弱操作 |

带有 |

同步操作 |

|

8.4.1. mmio 操作

mmio 操作是指定了 .mmio 限定符的内存操作。它通常在映射到对等 I/O 设备控制寄存器的内存位置上执行。它也可以用于线程之间的通信,但相对于非 mmio 操作而言,性能较差。

mmio 操作的语义含义无法精确定义,因为它是由底层 I/O 设备定义的。 从内存一致性模型的角度对 mmio 操作的语义进行形式化规范时,它等同于 strong 操作的语义。 但是,如果它在指定的范围内满足 CUDA 原子性要求,则它遵循一些特定于实现的属性。

写入操作始终执行,并且在指定的范围内永远不会合并。

-

读取操作始终执行,并且在指定的范围内不会被转发、预取、合并或允许命中任何缓存。

作为例外,在某些实现中,也可能会加载周围的位置。 在这种情况下,加载的数据量是特定于实现的,并且大小在 32 到 128 字节之间变化。

8.4.2. volatile 操作

volatile 操作是使用 .volatile 限定符指定的内存操作。 volatile 操作的语义等同于具有系统作用域的 relaxed 内存操作,但具有以下额外的特定于实现的约束

Volatile 指令 不会被 PTX 编译器拆分、合并或复制,也就是说,程序中 volatile 指令(不是操作)的数量会被保留。 硬件可能会合并和融合由多个不同的 volatile 指令发出的 volatile 操作,也就是说,程序中 volatile 操作的数量不会被保留。

Volatile 指令不会围绕其他 volatile 指令重新排序,但是这些指令的内存操作可能会彼此重新排序。

注意

PTX volatile 操作旨在供编译器将 CUDA C++ 以及其他共享 CUDA C++ volatile 语义的编程语言中的 volatile 读取和写入操作降低为 PTX。

由于 volatile 操作在系统作用域是 relaxed 的,并带有额外的约束,因此对于线程间同步,请优先使用其他 strong 读取或写入操作(例如 ld.relaxed.sys 或 st.relaxed.sys),这可能会提供更好的性能。

PTX volatile 操作不适用于 内存映射 I/O (MMIO),因为 volatile 操作不保留执行的内存操作的数量,并且可能以不确定的方式执行多于或少于请求的操作。 请改用 .mmio 操作,它严格保留执行的操作数量。

8.5. 作用域

每个 strong 操作都必须指定一个作用域,该作用域是可能与该操作直接交互并建立内存一致性模型中描述的任何关系的线程集合。 有四个作用域

作用域 |

描述 |

|---|---|

|

与当前线程在同一 CTA 中执行的所有线程的集合。 |

|

与当前线程在同一集群中执行的所有线程的集合。 |

|

当前程序中与当前线程在同一计算设备上执行的所有线程的集合。 这也包括主机程序在同一计算设备上调用的其他内核网格。 |

|

当前程序中所有线程的集合,包括主机程序在所有计算设备上调用的所有内核网格,以及构成主机程序本身的所有线程。 |

请注意,warp 不是作用域; CTA 是符合内存一致性模型中作用域条件的最小线程集合。

8.6. 代理

内存代理或代理是应用于内存访问方法的一个抽象标签。 当两个内存操作使用不同的内存访问方法时,它们被称为不同的代理。

操作类型中定义的内存操作使用通用内存访问方法,即通用代理。 其他操作(如纹理和表面)都使用不同的内存访问方法,也与通用方法不同。

需要代理栅栏来同步跨不同代理的内存操作。 尽管虚拟别名使用通用内存访问方法,但由于使用不同的虚拟地址的行为如同使用不同的代理,因此它们需要代理栅栏来建立内存排序。

8.7. Morally strong 操作

如果两个操作满足以下所有条件,则称它们相对于彼此是 morally strong 的

这些操作在程序顺序中相关(即,它们都由同一线程执行),或者每个操作都是 strong 的,并且指定了一个作用域,该作用域包括执行另一个操作的线程。

这两个操作都通过相同的代理执行。

如果两者都是内存操作,则它们完全重叠。

内存一致性模型中的大多数(但不是全部)公理都依赖于 morally strong 操作之间的关系。

8.7.1. 冲突和数据竞争

当至少其中一个操作是写入操作时,两个重叠的内存操作被称为冲突。

如果两个冲突的内存操作在因果顺序中不相关,并且它们不是 morally strong 的,则称它们处于数据竞争状态。

8.7.2. 混合尺寸数据竞争的限制

完全重叠的操作之间的数据竞争称为同尺寸数据竞争,而部分重叠的操作之间的数据竞争称为混合尺寸数据竞争。

如果 PTX 程序包含一个或多个混合尺寸数据竞争,则内存一致性模型中的公理不适用。 但是,这些公理足以描述仅具有同尺寸数据竞争的 PTX 程序的行为。

混合尺寸 RMW 操作的原子性

在任何有或没有混合尺寸数据竞争的程序中,对于每对重叠的原子操作 A1 和 A2,使得每个操作都指定了一个包含另一个操作的作用域,以下属性都成立: 由 A1 指定的读-修改-写操作要么在 A2 初始化之前完全执行,要么反之亦然。 此属性成立,而与两个操作 A1 和 A2 是部分重叠还是完全重叠无关。

8.8. 释放和获取模式

某些指令序列会产生参与内存同步的模式,如下所述。 释放模式使来自当前线程1的先前操作对来自其他线程的某些操作可见。 获取模式使来自其他线程的某些操作对来自当前线程的后续操作可见。

位置 M 上的释放模式包括以下之一

-

位置 M 上的释放操作

例如:

st.release [M];或atom.acq_rel [M];或mbarrier.arrive.release [M]; -

或位置 M 上的释放操作,后跟程序顺序中位置 M 上的 strong 写入操作

例如:

st.release [M];st.relaxed [M]; -

或内存栅栏,后跟程序顺序中位置 M 上的 strong 写入操作

例如:

fence; st.relaxed [M];

由释放模式建立的任何内存同步仅影响在该模式中第一个指令之前的程序顺序中发生的操作。

位置 M 上的获取模式包括以下之一

-

位置 M 上的获取操作

例如:

ld.acquire [M];或atom.acq_rel [M];或mbarrier.test_wait.acquire [M]; -

或位置 M 上的 strong 读取操作,后跟程序顺序中位置 M 上的获取操作

例如:

ld.relaxed [M]; ld.acquire [M]; -

或位置 M 上的 strong 读取操作,后跟程序顺序中的内存栅栏

例如:

ld.relaxed [M]; fence;

由获取模式建立的任何内存同步仅影响在该模式中最后一个指令之后的程序顺序中发生的操作。

1 对于释放和获取模式,此效果通过因果顺序的传递性进一步扩展到其他线程中的操作。

8.9. 内存操作的排序

每个线程执行的操作序列被捕获为程序顺序,而跨线程的内存同步被捕获为因果顺序。 内存操作的副作用对其他内存操作的可见性被捕获为通信顺序。 内存一致性模型定义了通信顺序与因果顺序和程序顺序之间不允许存在的矛盾。

8.9.1. 程序顺序

程序顺序将线程执行的所有操作与顺序处理器执行相应 PTX 源中指令的顺序相关联。 它是一个传递关系,在线程执行的操作上形成总顺序,但不关联来自不同线程的操作。

8.9.1.1. 异步操作

某些 PTX 指令(cp.async、cp.async.bulk、cp.reduce.async.bulk、wgmma.mma_async 的所有变体)执行的操作相对于执行该指令的线程是异步的。 这些异步操作在同一线程中的先前指令之后排序(wgmma.mma_async 的情况除外),但它们不属于该线程的程序顺序。 相反,它们提供较弱的排序保证,如指令描述中所述。

例如,作为 cp.async 一部分执行的加载和存储操作彼此之间是有序的,但与同一线程启动的任何其他 cp.async 指令的加载和存储操作无关,也与线程随后发出的任何其他指令的加载和存储操作无关,但 cp.async.commit_group 或 cp.async.mbarrier.arrive 除外。 由 cp.async.mbarrier.arrive 指令执行的异步 mbarrier arrive-on 操作相对于同一线程启动的所有先前 cp.async 操作执行的内存操作排序,但与线程发出的任何其他指令的内存操作无关。 作为 cp.async.bulk 和 cp.reduce.async.bulk 指令的所有变体一部分的隐式 mbarrier complete-tx 操作仅相对于同一异步指令执行的内存操作排序,并且特别地,它不传递性地建立与来自发出线程的先前指令的排序。

8.9.2. 观察顺序

观察顺序通过可选的原子读-修改-写操作序列将写入 W 与读取 R 相关联。

如果满足以下条件,则写入 W 在观察顺序中先于读取 R

R 和 W 是 morally strong 的,并且 R 读取由 W 写入的值,或者

对于某些原子操作 Z,W 在观察顺序中先于 Z,并且 Z 在观察顺序中先于 R。

8.9.3. Fence-SC 顺序

Fence-SC 顺序是一个运行时确定的非循环偏序,它关联每对 morally strong fence.sc 操作。

8.9.4. 内存同步

不同线程执行的同步操作在此处描述的运行时彼此同步。 这种同步的效果是在线程之间建立因果顺序。

如果 fence.sc 操作 X 在 Fence-SC 顺序中先于 fence.sc 操作 Y,则 X 与 Y 同步。

bar{.cta}.sync 或 bar{.cta}.red 或 bar{.cta}.arrive 操作与在同一栅栏上执行的 bar{.cta}.sync 或 bar{.cta}.red 操作同步。

barrier.cluster.arrive操作与barrier.cluster.wait操作同步。如果 X 中的写入操作在观察顺序中先于 Y 中的读取操作,并且 X 中的第一个操作和 Y 中的最后一个操作是 morally strong 的,则释放模式 X 与获取模式 Y 同步。

API 同步

同步关系也可以通过某些 CUDA API 建立。

在 CUDA 流中排队的任务的完成与同一流中后续任务(如果有)的开始同步。

出于上述目的,在流中记录或等待 CUDA 事件,或由于

cudaStreamLegacy而导致插入跨流栅栏,即使没有直接的副作用,也会在关联的流中排队任务。 事件记录任务与匹配的事件等待任务同步,栅栏到达任务与匹配的栅栏等待任务同步。CUDA 内核的开始与内核中所有线程的开始同步。 内核中所有线程的结束与内核的结束同步。

CUDA 图的开始与图中所有源节点的开始同步。 CUDA 图中所有 sink 节点的完成与图的完成同步。 图节点的完成与所有具有直接依赖关系的节点的开始同步。

调用 CUDA API 以排队任务的开始与任务的开始同步。

排队到流的最后一个任务(如果有)的完成与从

cudaStreamSynchronize返回同步。 最近排队的匹配事件记录任务(如果有)的完成与从cudaEventSynchronize返回同步。 同步 CUDA 设备或上下文的行为如同同步上下文中的所有流,包括已销毁的流。从 API 返回

cudaSuccess以查询 CUDA 句柄(例如流或事件)的行为与从匹配的同步 API 返回的行为相同。

除了建立同步关系外,上述 CUDA API 同步机制也参与代理保留的基本因果顺序。

8.9.5. 因果顺序

因果顺序捕获内存操作如何通过同步操作在线程之间变得可见。 “因果性”公理使用此顺序来约束读取操作可以从中读取值的写入操作集。

因果顺序中的关系主要包括基本因果顺序1 中的关系,后者是运行时确定的传递顺序。

基本因果顺序

如果满足以下条件,则操作 X 在基本因果顺序中先于操作 Y

X 在程序顺序中先于 Y,或者

X 与 Y 同步,或者

-

对于某些操作 Z,

X 在程序顺序中先于 Z,并且 Z 在基本因果顺序中先于 Y,或者

X 在基本因果顺序中先于 Z,并且 Z 在程序顺序中先于 Y,或者

X 在基本因果顺序中先于 Z,并且 Z 在基本因果顺序中先于 Y。

代理保留的基本因果顺序

如果内存操作 X 在基本因果顺序中先于内存操作 Y,并且满足以下条件,则内存操作 X 在代理保留的基本因果顺序中先于内存操作 Y

X 和 Y 使用通用代理对同一地址执行操作,或者

X 和 Y 使用相同的代理对同一地址执行操作,并且由相同的线程块执行,或者

X 和 Y 是别名,并且从 X 到 Y 的基本因果路径上存在别名代理栅栏。

因果顺序

因果顺序将基本因果顺序与一些非传递关系结合起来,如下所示

如果满足以下条件,则操作 X 在因果顺序中先于操作 Y

X 在代理保留的基本因果顺序中先于 Y,或者

对于某些操作 Z,X 在观察顺序中先于 Z,并且 Z 在代理保留的基本因果顺序中先于 Y。

1 基本因果顺序的传递性解释了同步操作的“累积性”。

8.9.6. 一致性顺序

存在一个运行时确定的关联重叠写入操作的偏序传递顺序,称为一致性顺序1。 如果两个重叠的写入操作是 morally strong 的,或者它们在因果顺序中相关,则它们在一致性顺序中相关。 如果两个重叠的写入操作处于数据竞争状态,则它们在一致性顺序中不相关,这导致了一致性顺序的偏序性质。

1 一致性顺序无法直接观察到,因为它完全由写入操作组成。 它可以间接观察到,通过其在约束读取操作可以从中读取的候选写入操作集中的使用。

8.9.7. 通信顺序

通信顺序是一个运行时确定的非传递顺序,它将写入操作与其他重叠的内存操作相关联。

如果读取 R 返回由 W 写入的任何字节的值,则写入 W 在通信顺序中先于重叠的读取 R。

如果 W 在一致性顺序中先于 W’,则写入 W 在通信顺序中先于写入 W’。

如果对于 R 和 W 都访问的任何字节,R 返回由在一致性顺序中先于 W 的写入 W’ 写入的值,则读取 R 在通信顺序中先于重叠的写入 W。

通信顺序捕获内存操作的可见性——当内存操作 X1 在通信顺序中先于内存操作 X2 时,称 X1 对 X2 可见。

8.10. 公理

8.10.1. 一致性

如果写入 W 在因果顺序中先于重叠的写入 W’,则 W 必须在一致性顺序中先于 W’。

8.10.2. Fence-SC

Fence-SC 顺序不能与因果顺序相矛盾。 对于一对 morally strong 的 fence.sc 操作 F1 和 F2,如果 F1 在因果顺序中先于 F2,则 F1 必须在 Fence-SC 顺序中先于 F2。

8.10.3. 原子性

单副本原子性

冲突的 morally strong 操作以单副本原子性执行。 当读取 R 和写入 W 是 morally strong 的时,对于 R 和 W 访问的字节集,以下两个通信不能同时存在于同一执行中

R 从 W 读取任何字节。

R 从任何在一致性顺序中先于 W 的写入 W’ 读取任何字节。

读-修改-写 (RMW) 操作的原子性

当原子操作 A 和写入 W 重叠并且是 morally strong 的时,对于 A 和 W 访问的字节集,以下两个通信不能同时存在于同一执行中

A 从在一致性顺序中先于 W 的写入 W’ 读取任何字节。

A 在一致性顺序中跟随 W。

Litmus 测试 1

.global .u32 x = 0;

|

|

T1 |

T2 |

A1: atom.sys.inc.u32 %r0, [x];

|

A2: atom.sys.inc.u32 %r0, [x];

|

FINAL STATE: x == 2

|

|

当操作是 morally strong 的时,原子性得到保证。

Litmus 测试 2

.global .u32 x = 0;

|

|

T1 |

T2(在不同的 CTA 中) |

A1: atom.cta.inc.u32 %r0, [x];

|

A2: atom.gpu.inc.u32 %r0, [x];

|

FINAL STATE: x == 1 OR x == 2

|

|

如果操作不是 morally strong 的,则原子性不能得到保证。

8.10.4. 凭空产生

值可能不会“凭空产生”:执行不能以推测方式生成值,以至于推测通过指令依赖性和线程间通信链变得自我满足。 这既符合程序员的直觉,也符合硬件的实际情况,但在执行形式化分析时必须明确说明。

Litmus 测试:加载缓冲

.global .u32 x = 0;

.global .u32 y = 0;

|

|

T1 |

T2 |

A1: ld.global.u32 %r0, [x];

B1: st.global.u32 [y], %r0;

|

A2: ld.global.u32 %r1, [y];

B2: st.global.u32 [x], %r1;

|

FINAL STATE: x == 0 AND y == 0

|

|

称为 “LB”(加载缓冲)的 litmus 测试检查可能凭空产生的此类禁止值。 两个线程 T1 和 T2 各自从第一个变量读取,并将观察到的结果复制到第二个变量中,其中第一个变量和第二个变量在线程之间交换。 如果每个变量最初都为零,则最终结果也应为零。 如果 A1 从 B2 读取,而 A2 从 B1 读取,则通过此示例中内存操作传递的值形成一个循环:A1->B1->A2->B2->A1。 只有值 x == 0 和 y == 0 才允许满足此循环。 如果此示例中的任何内存操作要推测性地将不同的值与相应的内存位置关联,则此类推测将变得自我实现,因此是被禁止的。

8.10.5. 每位置顺序一致性

在任何成对 morally strong 的重叠内存操作集合中,通信顺序不能与程序顺序相矛盾,即,重叠操作之间的程序顺序和通信顺序中 morally strong 关系的串联不能导致循环。 这确保了成对 morally strong 操作的每个程序切片都是严格顺序一致的。

Litmus 测试:CoRR

.global .u32 x = 0;

|

|

T1 |

T2 |

W1: st.global.relaxed.sys.u32 [x], 1;

|

R1: ld.global.relaxed.sys.u32 %r0, [x];

R2: ld.global.relaxed.sys.u32 %r1, [x];

|

IF %r0 == 1 THEN %r1 == 1

|

|

litmus 测试 “CoRR”(一致性读取-读取)演示了此保证的一个结果。 线程 T1 在位置 x 上执行写入 W1,线程 T2 在同一位置 x 上执行两个(或无限序列的)读取 R1 和 R2。 除了模拟初始值的写入之外,没有在 x 上执行其他写入。 操作 W1、R1 和 R2 成对是 morally strong 的。 如果 R1 从 W1 读取,则后续读取 R2 也必须观察到相同的值。 如果 R2 观察到 x 的初始值,则这将在通信顺序中形成与线程 T2 中的程序顺序 R1->R2 相矛盾的 morally-strong 关系序列 R2->W1->R1。 因此,R2 在这样的执行中不能读取 x 的初始值。

8.10.6. 因果性

通信顺序中的关系不能与因果顺序相矛盾。 这约束了读取操作可以从中读取的候选写入操作集

如果读取 R 在因果顺序中先于重叠的写入 W,则 R 不能从 W 读取。

如果写入 W 在因果顺序中先于重叠的读取 R,则对于 R 和 W 都访问的任何字节,R 不能从任何在一致性顺序中先于 W 的写入 W’ 读取。

Litmus 测试:消息传递

.global .u32 data = 0;

.global .u32 flag = 0;

|

|

T1 |

T2 |

W1: st.global.u32 [data], 1;

F1: fence.sys;

W2: st.global.relaxed.sys.u32 [flag], 1;

|

R1: ld.global.relaxed.sys.u32 %r0, [flag];

F2: fence.sys;

R2: ld.global.u32 %r1, [data];

|

IF %r0 == 1 THEN %r1 == 1

|

|

称为 “MP”(消息传递)的 litmus 测试代表了典型同步算法的本质。 绝大多数有用的程序都可以简化为此模式的顺序应用。

线程 T1 首先写入数据变量,然后写入标志变量,而第二个线程 T2 首先从标志变量读取,然后从数据变量读取。 标志上的操作是 morally strong 的,并且每个线程中的内存操作都由 fence 分隔,并且这些 fence 是 morally strong 的。

如果 R1 观察到 W2,则释放模式 “F1; W2” 与获取模式 “R1; F2” 同步。 这建立了因果顺序 W1 -> F1 -> W2 -> R1 -> F2 -> R2。 然后,因果性公理保证 R2 不能从任何在一致性顺序中先于 W1 的写入读取。 在此示例中没有任何其他写入的情况下,R2 必须从 W1 读取。

Litmus 测试:CoWR

// These addresses are aliases

.global .u32 data_alias_1;

.global .u32 data_alias_2;

|

T1 |

W1: st.global.u32 [data_alias_1], 1;

F1: fence.proxy.alias;

R1: ld.global.u32 %r1, [data_alias_2];

|

%r1 == 1

|

虚拟别名需要沿同步路径的别名代理栅栏。

Litmus 测试:存储缓冲

称为 “SB”(存储缓冲)的 litmus 测试演示了由 fence.sc 强制执行的顺序一致性。 线程 T1 写入第一个变量,然后读取第二个变量的值,而第二个线程 T2 写入第二个变量,然后读取第一个变量的值。 每个线程中的内存操作都由 fence.sc 指令分隔,并且这些 fence 是 morally strong 的。

.global .u32 x = 0;

.global .u32 y = 0;

|

|

T1 |

T2 |

W1: st.global.u32 [x], 1;

F1: fence.sc.sys;

R1: ld.global.u32 %r0, [y];

|

W2: st.global.u32 [y], 1;

F2: fence.sc.sys;

R2: ld.global.u32 %r1, [x];

|

%r0 == 1 OR %r1 == 1

|

|

在任何执行中,F1 要么在 Fence-SC 顺序中先于 F2,要么反之亦然。 如果 F1 在 Fence-SC 顺序中先于 F2,则 F1 与 F2 同步。 这在 W1 -> F1 -> F2 -> R2 中建立了因果顺序。 因果性公理确保 R2 不能从任何在一致性顺序中先于 W1 的写入读取。 在没有对该变量进行任何其他写入的情况下,R2 必须从 W1 读取。 类似地,在 F2 在 Fence-SC 顺序中先于 F1 的情况下,R1 必须从 W2 读取。 如果此示例中的每个 fence.sc 都被 fence.acq_rel 指令替换,则不能保证此结果。 可能存在执行,其中来自每个线程的写入对另一个线程保持未观察到,即,可能存在执行,其中 R1 和 R2 都分别返回变量 y 和 x 的初始值 “0”。

9. 指令集

9.1. 指令描述的格式和语义

本节介绍每个 PTX 指令。 除了指令的名称和格式外,还描述了语义,并附带一些示例,试图展示指令的几种可能的实例化。

9.2. PTX 指令

PTX 指令通常有零到四个操作数,外加一个可选的保护谓词,它出现在 opcode 左侧的 @ 符号之后

@p opcode;@p opcode a;@p opcode d, a;@p opcode d, a, b;@p opcode d, a, b, c;

对于创建结果值的指令,d 操作数是目标操作数,而 a、b 和 c 是源操作数。

setp 指令写入两个目标寄存器。我们使用 | 符号分隔多个目标寄存器。

setp.lt.s32 p|q, a, b; // p = (a < b); q = !(a < b);

对于某些指令,目标操作数是可选的。可以使用下划线 (_) 表示的位桶操作数来代替目标寄存器。

9.3. 条件执行

在 PTX 中,谓词寄存器是虚拟的,并且类型说明符为 .pred。因此,谓词寄存器可以声明为

.reg .pred p, q, r;

所有指令都有一个可选的保护谓词,用于控制指令的条件执行。指定条件执行的语法是在指令前加上 @{!}p,其中 p 是谓词变量,可以选择取反。没有保护谓词的指令会无条件执行。

谓词最常设置为 setp 指令执行比较的结果。

例如,考虑以下高级代码

if (i < n)

j = j + 1;

这可以用 PTX 写成

setp.lt.s32 p, i, n; // p = (i < n)

@p add.s32 j, j, 1; // if i < n, add 1 to j

要获得条件分支或条件函数调用,请使用谓词来控制分支或调用指令的执行。要将上述示例实现为真正的条件分支,可以使用以下 PTX 指令序列

setp.lt.s32 p, i, n; // compare i to n

@!p bra L1; // if False, branch over

add.s32 j, j, 1;

L1: ...

9.3.1. 比较

9.3.1.1. 整数和位大小比较

有符号整数比较是传统的 eq(等于)、ne(不等于)、lt(小于)、le(小于或等于)、gt(大于)和 ge(大于或等于)。无符号比较是 eq、ne、lo(更低)、ls(更低或相同)、hi(更高)和 hs(更高或相同)。位大小比较是 eq 和 ne;排序比较未为位大小类型定义。

表 21 显示了有符号整数、无符号整数和位大小类型的运算符。

含义 |

有符号运算符 |

无符号运算符 |

位大小运算符 |

|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

不适用 |

|

|

|

不适用 |

|

|

|

不适用 |

|

|

|

不适用 |

9.3.1.2. 浮点比较

有序浮点比较是 eq、ne、lt、le、gt 和 ge。如果任一操作数是 NaN,则结果为 False。表 22 列出了浮点比较运算符。

含义 |

浮点运算符 |

|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

为了辅助存在 NaN 值时的比较操作,提供了无序浮点比较:equ、neu、ltu、leu、gtu 和 geu。如果两个操作数都是数值(不是 NaN),则比较的结果与其有序对应项相同。如果任一操作数是 NaN,则比较的结果为 True。

表 23 列出了接受 NaN 值的浮点比较运算符。

含义 |

浮点运算符 |

|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

为了测试 NaN 值,提供了两个运算符 num(numeric)和 nan(isNaN)。如果两个操作数都是数值(不是 NaN),则 num 返回 True,如果任一操作数是 NaN,则 nan 返回 True。表 24 列出了测试 NaN 值的浮点比较运算符。

含义 |

浮点运算符 |

|---|---|

|

|

|

|

9.3.2. 操作谓词

谓词值可以使用以下指令进行计算和操作:and、or、xor、not 和 mov。

谓词和整数值之间没有直接转换,也没有直接加载或存储谓词寄存器值的方法。但是,setp 可以用于从整数生成谓词,而基于谓词的选择 (selp) 指令可以用于基于谓词的值生成整数值;例如

selp.u32 %r1,1,0,%p; // convert predicate to 32-bit value

9.4. 指令和操作数的类型信息

类型化指令必须具有类型大小修饰符。例如,add 指令需要类型和大小信息才能正确执行加法运算(有符号、无符号、浮点、不同大小),此信息必须指定为操作码的后缀。

例子

.reg .u16 d, a, b;

add.u16 d, a, b; // perform a 16-bit unsigned add

某些指令需要多个类型大小修饰符,最值得注意的是数据转换指令 cvt。它需要为结果和源分别指定类型大小修饰符,并且这些修饰符的顺序与操作数相同。例如

.reg .u16 a;

.reg .f32 d;

cvt.f32.u16 d, a; // convert 16-bit unsigned to 32-bit float

通常,操作数的类型必须与相应的指令类型修饰符一致。操作数和指令类型一致性的规则如下